# NOTICE WARNING CONCERNING COPYRIGHT RESTRICTIONS:

The copyright law of the United States (title 17, U.S. Code) governs the making of photocopies or other reproductions of copyrighted material. Any copying of this document without permission of its author may be prohibited by law.

# EVALUATION OF ALTERNATIVE COMPUTER ARCHITECTURES

M.R. Barbacci<sup>1</sup>, W.E. Burr<sup>2</sup>, S.H. Fuller<sup>1</sup>, and D.P. Siewiorek<sup>1</sup> (Eds.)

Department of Computer Science Carnegie-Mellon University Pittsburgh Pa. 15213

February 12, 1977

The Computer Family Architecture project was organized and supervised by the Army Electronics Command, Fort Monmouth, N.J. and the Naval Research Laboratory, Washington D.C. The work described here was supported in part by the Defense Advanced Research Projects Agency (ARPA) under contract F44620-73-C-0074, in part by the National Science Foundation under grant GJ 32758X, and in part by the Army Research Office under grant DAAG29-76-G-0299.

<sup>1</sup> Also with the Naval Research Laboratory, Washington, D.C.

<sup>2</sup> U.S. Army Electronics Command, Ft. Monmouth, N.J.

#### Abstract

The Computer Family Architecture (CFA) Selection Committee was organized to select a proven, well-known computer architecture, in addition to several widely used military computer architectures, as the basis of the future series of Military Computer Family (MCF) computers. The set of four papers that make up this report provide an overview of the work of the CFA Committee and a detailed discussion of the technical methods used to quantitatively evaluate the alternative computer architectures under consideration.

As the first paper describes, support software availability, life cycle costs, and architecture licensing, in addition to architectural efficiency, were considered in the final evaluation process. As a result of this process, the CFA Committee ranked the three architecture finalists in the following order: the DEC PDP-11, the IBM System/370, and the Interdata 8/32. The MCF project is now working on the specification of a new standard architecture for military applications based on the PDP-11. In addition, the MCF project is working on more clearly specifying the most widely used existing military computer architectures to enable future re-implementations of these architectures in new technologies.

#### Papers in this Technical Report

1. Burr, W.E., A.H. Coleman, and W.R. Smith: <u>Summary of the Final Report of the</u> <u>Computer Family Architecture Selection Committee</u>

2\*. Fuller, S.H., W.E. Burr, and S.H. Stone: <u>Initial Selection and Screening of the CFA</u> <u>Candidate Computer Architectures</u>

3\*. Fuller, S.H., W.E. Burr, P. Shaman, and D. Lamb: <u>Evaluation of Computer Architectures</u> via <u>Test Programs</u> 4\*. Barbacci, M.R., D.P. Siewiorek, R. Gordon, R. Howbrigg, and S. Zuckerman: <u>Architecture Research Facility: ISP Descriptions, Simulation, and Data Collection</u>

<sup>\*</sup> These papers will appear in the 1977 National Computer Conference, Dallas, Texas, June 13-16, 1977.

## SUMMARY OF THE FINAL REPORT OF THE ARMY/NAVY COMPUTER FAMILY ARCHITECTURE SELECTION COMMITTEE

William E. Burr U.S. Army Electronics Command Fort Monmouth, N.J.

Aaron H. Coleman U.S. Army Electronics Command Fort Monmouth, N.J.

.

.

and

William R. Smith Naval Research Laboratory Washington, D.C.

-

# TABLE OF CONTENTS

# SECTION

PAGE

| 1 | Introd | duction | ۱       | ••     |        |       | • •  | •   |     | ••• | • | •   | • | • • |     |   | •   | • | •          | •   | •   | • | . 1 |  |

|---|--------|---------|---------|--------|--------|-------|------|-----|-----|-----|---|-----|---|-----|-----|---|-----|---|------------|-----|-----|---|-----|--|

| 2 | Backg  | round   |         |        |        | •••   | • •  | •   | • • |     | • | •   | • | •   |     | • | •   | • | •          | •   | •   | • | . 2 |  |

| Э | The C  | FA/M    | CF Pro  | ject   |        |       |      |     |     |     |   |     |   |     | •   | • | •   | • | •          | •   |     | • | 4   |  |

| 4 | The C  | FA Se   | lection | Comn   | nittee | ÷.    | • •  | ٠   |     | •   | • | •   | • | ••• | •   | • | •   | • | •          | •   | •   | • | 5   |  |

| 5 | Candic | date A  | rchited | tures  | • •    |       |      | •   | ••• |     |   | •   | • | • • | •   | • | •   | • | •          | •   | •   | • | 6   |  |

| 6 | Select | tion Pr | ocedur  | е.,    | • •    |       | •••  | • • |     |     |   | •   | • |     | ••• |   |     |   | •          |     | •   | • | 7   |  |

|   | 6.1    | Initia  | Scree   | ning   |        |       | •••  | •   | ••• |     |   | •   | • | ••• |     | • | •   | • | •          |     |     | • | 7   |  |

|   | 6.2    | Final   | Candid  | ates E | valua  | ation |      | •   |     |     | • |     | • |     |     | • | •   | • | •          |     | •   | • | 9   |  |

|   | 6.3    | Final   | Selecti | on/Re  | comm   | nend  | atio | 15. | •   | • • | • | • • | • | •   | •   |   | • • |   | •          | ٠   | •   | • | 16  |  |

| 7 | Conclu | usions  | • • •   | • • •  |        |       |      | • • | •   | ••• | • | •   |   | •   | •   | • | •   | • | •          | •   | • • | , | 17  |  |

| 8 | Appen  | ndix    |         |        |        | · •   |      |     | •   |     | • | •   |   |     |     |   | •   | • | <b>.</b> . | • • |     |   | 19  |  |

#### <u>Abstract</u>

An Army/Navy Computer Family Architecture (CFA) Selection Committee, comprising 10 Army and 17 Navy organizations was organized by the Naval Research Laboratory and the Army Electronics Command in 1975 to select a proven, well-known computer architecture to be the basis of a Military Computer Family (MCF). The Selection Committee met five times in the period between October, 1975, and August, 1976, and evaluated nine computer architecture candidates in accordance with criteria established by the Committee. The Committee applied a preliminary screening process to select three candidates (IBM S/370, DEC PDP-11, and Interdata 8/32) for more intensive evaluation. This final evaluation process considered experimentally determined architectural efficiency, support software availability, life cycle cost, and architecture licensing. As a result of this process, the Committee ranked the three architecture finalists in the following order:

> 1. PDP-11 2. S/370 3. 8/32

### 1. Introduction

This report describes the work performed by an Army/Navy Committee, representing 10 Army and 17 Navy organizations, to select a Computer Family Architecture (CFA) for use with a proposed software compatible family of military computers and associated systems/support software. This family is known as the Military Computer Family (MCF).

This report summarizes the contents of a full report on the work of the CFA Selection Committee (i.e., "Final Report of the CFA Selection Committee"). References

**i-1**

to this full report will be made herein, in accordance with the table of contents shown in the Appendix.

#### 2. Background

The Department of Defense is spending over six billion dollars yearly for ADP systems. A large portion of this goes for acquisition of militarized computers and associated software that are used in tactical and strategic areas. Traditionally, these computers have been specified by the individual organizations (military project offices or commercial contractors) responsible for the development of each system. More often than not, computer selections are based upon local schedule, funding, or profit considerations, rather than the impact that the selection would have on long range hardware/software logistics costs. The result has been that the large number of types of computers used in Army and Navy systems are causing serious problems in the development and maintenance of software for those systems.

Military computers are usually procured as integral components of larger systems (e.g., radars, missile systems); the hardware issues have historically been given more attention than the logistics of the software, and in consequence, military computers normally have only the most primitive sort of support software. The development cycles for weapons systems are generally long enough (5 to 10 years) that the military computers in these systems are often obsolete before they are ever delivered to the Field Army or the Fleet. Past computer standardization efforts in the military have concentrated on hardware packaging or obscure architectures of such small market that there has been no incentive for the computer industry at large to invest in developing software and hardware compatible with these computers. The end

result of these conditions is that the military pays over and over for development of computer systems that frequently fall far short of performance expectations.

This can be contrasted with the situation in the commercial OEM (original equipment manufacturer) marketplace. Here computers are produced for the much larger commercial market by the thousands or even the tens of thousands. A number of manufacturers such as DEC, Data General, and Interdata have software compatible product lines, covering a wide range of processors of varying capabilities. Due to fierce competitive market pressures, system deficiencies are corrected, or the systems disappear. New products are developed much more quickly, and full advantage is taken of the advances in semiconductor device technology. Finally, due to the much larger user bases of commercial computers, and the competitive pressures of the marketplace, the support software bases of successful commercial computers are usually far superior to their military equivalents and are frequently improved or augmented by organizations seeking a share of this market.

A solution to many of the software problems with contemporary military computers would be to produce a family of software-compatible militarized computers. Moreover, if such a family were based upon a proven, commercial instruction-set architecture, then it would be possible to capture a good mature support software base, and to be certain that any architectural shortcomings were known and recognized. As the commercial system evolved, and the architecture was extended to meet the competition, the military computer family could also take advantage of these same extensions. Adhering to an established family in this way would avoid the architectural mavericks that limited-production military computers are prone to be.

### 3. The CFA/MCF Project

Since early 1975, the Center for Tactical Computer Sciences (CENTACS) of the U. S. Army Electronics Command and the Naval Air Systems Command (NAVAIR) have been supporting a cooperative Army/Navy effort to develop such a family of military computers, based upon a common instruction-set architecture.

The fundamental premise of the MCF project is that software compatibility should be achieved by the adoption of an existing, proven computer architecture for the MCF, thereby minimizing the risks inherent in the design of a new computer architecture and permitting the "capture" of an existing and evolving software base. this context, computer architecture is distinguished from implementation Inconsiderations, and is defined as the structure of the computer which a machine level programmer needs to know in order to write all programs which will run correctly on the computer. For example, the architecture of the IBM S/370 is defined in the IBM System/370 Principles of Operations Manual. There are many implementations of the architecture (370-158, 370-168, etc.), but only one architecture, and every implementation will execute the same software. Another premise upon which the Army/Navy cooperative effort is based is the goal of software transportability from prior generation military computers to the MCF, most probably via emulation. In other words, the Army and Navy cannot abandon its investment in existing software. There is a strong analogy here with IBM's continued support of such machines as the 1401 and the 7090 via emulation, when the 360 family was introduced.

The first task of the MCF project was the selection of the CFA. CENTACS and the Naval Research Laboratory cooperated to lead that effort, and the following sections of this report describe how that selection was made.

The second task of the project is to develop a System Implementation Plan, which in a commercial organization would probably be called a product plan, to define the form, fit, and function characteristics of the MCF and the individual family members. The instruction-set architecture of the processors, not the detailed logic design will be specified, so that various military equipment manufacturers (in general, <u>not</u> the manufacturer of the commercial version of the CFA) will be able to independently develop MCF members to meet the form, fit, and function requirements of the MCF, and to run the CFA instruction set. This approach will permit multiple sources for the various family members, and will allow manufacturers to take maximum advantage of rapidly developing semiconductor technology. The goal is a line of plug-compatible modules that can be interconnected as computer systems in a variety of configurations, to meet a wide range of performance/ application requirements.

A similar Support Software Implementation Plan contract is planned for FY 1978. This plan will attempt to take maximum advantage of the existing support software base for the selected CFA.

#### 4. The CFA Selection Committee

The mechanism for selecting the CFA was a joint Army/Navy Selection Committee. In order to achieve a wide representation of military computer requirements in this effort, letters were sent to Army and Navy Laboratories, System Centers, and Project Managers, inviting them to nominate "candidate" architectures, and to participate in the CFA selection process as members of the CFA Selection Committee. Ten Army and 17 Navy organizations assigned representatives to the Selection Committee, which was active between October 1975, and August 1976. The

members and officers of the Selection Committee are given in Volume I of the Final Report.

Of the several procedural rules adopted by the Committee, the most important was the requirement for a 2/3 vote of the members present to carry a committee motion.

#### 5. Candidate Architectures

The basic mechanism for deciding which architectures should be considered by the committee was to ask Army and Navy organizations to nominate candidate architectures. These nominations were augmented by the Committee in its early meetings. The architectures which were considered by the Committee are:

> Burroughs B-6700 DEC PDP-11 IBM S/370 Interdata 8/32 Litton An/GYK-12 NOVA/ROLM 1662 Systems Engineering Laboratories SEL 32 Univac AN/UYK-7 Univac AN/UYK-20

On the list of candidates the S/370 and the B6700 are large scale commercial data processing type architectures. The PDP-11, SEL-32, 8/32, and the NOVA are classical OEM type minicomputers, and the AN/GYK-12, AN/UYK-7, and the AN/UYK-20 are three of the most widely used military computers.

Although the above list of architectures is not all inclusive, most of the Army and Navy organizations who nominated candidates went through their own internal screening process, considering a much wider selection of architectures prior to making their nominations. As a result, the nine architectures considered by the Committee

represent the best candidates for a family of computers for military applications, according to the consensus of over two dozen Army and Navy organizations.

## 6. Selection Procedure

It was apparent to the Committee after much discussion, that there were certain key, critical characteristics that should be well satisfied by the selected CFA. Further, it became apparent that it made sense to perform an initial screening and ranking of the candidates, based on these characteristics, so that the obviously least acceptable candidates could be discarded and those with the most potential could be retained and investigated much more thoroughly. An initial screening process was therefore devised to select several "best final candidates" for more detailed evaluation.

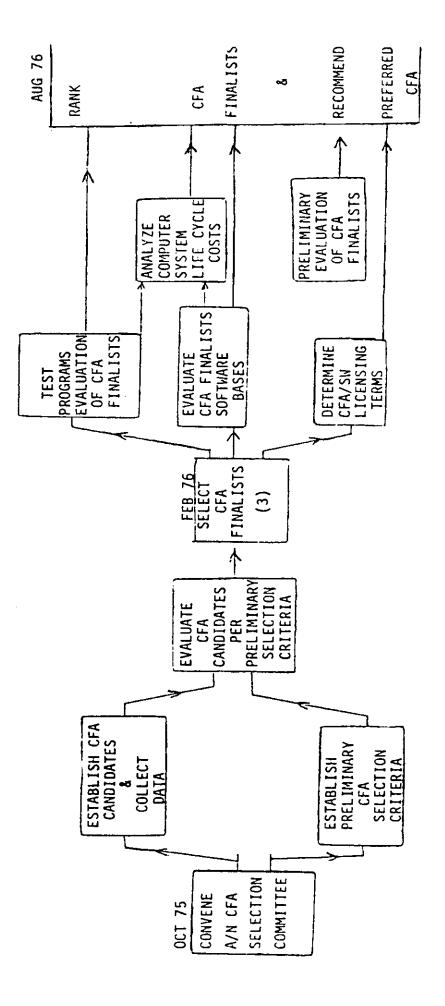

After the initial screening process was completed, the three final candidates were subjected to a test program experiment to measure the efficiency of the architectures. The support software bases of the three architectures were studied, and life-cycle cost models were constructed to determine if one of the three architectures had a decisive economic advantage. Finally, the manufacturers were contacted to determine the conditions under which they would be willing to license their architectures for production by military vendors. This process is illustrated in Figure 1, and is described in more detail below.

# 6.1. Initial Screening

The Selection Committee decided to select the final candidate architectures from the initial list by means of two kinds of criteria. The first kind of criteria, which served as pass/fail tests of architectural adequacy, were called "absolute criteria". The committee planned to eliminate all architectures which did not completely satisfy

these criteria. Absolute criteria included such requirements as a satisfactory protection mechanism, and a virtual to physical address translation mechanism. The second kind of criteria were caled "quantitative criteria". The quantitative criteria were intended to provide a relative ranking of the architectures in terms of characteristics which the committee believed were important measures of a computer architecture. Quantitative criteria included such characteristics as the size of the physical address space, the size of the virtual address space, the number of bits which had to be moved to save that state of the machine under various circumstances, and the size of the installed user base. A listing and very brief description of the absolute and quantitative criteria are shown in Table 1. The reader should see Volume II of the CFA Committee Final Report for a detailed discussion of these criteria. Each quantitative criterion was assigned a weighing factor by each committee for each criterion. The quantitative criteria scores for each candidate were normalized, weighted, and summed to give a composite figure of merit for each architecture.

Subcommittees were created to evaluate each architecture, in terms of the absolute and quantitative criteria. A meeting of the full committee was then devoted principaly to verifying the consistency and correctness of the evaluations of the candidate architectures. In addition, the results of this evaluation were audited by a consultant to ensure the consistency and correctness of the evaluation.

A principal difficulty in making the evaluations was the imprecision of most of the reference manuals of the candidate architectures, requiring frequent communication with the manufacturers in some cases. Certain of the manuals, as typified by the IBM S/370 Principals of Operation Manual, appeared to be complete and precise definitions

of an architecture. Others left essential architectural details ambiguously defined or not defined at all.

The results of the absolute and quantitative criteria evaluations are summarized in Table 2. The PDP-11 and the IBM S/370 were the only two architectures which clearly passed all the absolute criteria, and they also were among the top three in the quantitative criteria evaluation. The Interdata 8/32 was also selected as a finalist on the basis of its very strong showing on the quantitative criteria, despite a nagging technical uncertainty concerning the state of the machine after interrupts, which the committee was never able to resolve to its own satisfaction.

The reader is cautioned that the application of these criteria requires a great deal of interpretation. The Selection Committee went to some considerable effort to arrive at comparable interpretations for each architecture. It may not be at all obvious from the simple definitions presented here, how the actual values used by the committee were calculated. This is documented in detail in Volume II of the CFA Committee Final Report, and the interested reader should refer to Volume II.

6.2. Final Candidates Evaluation

#### Architecture Efficiency Evaluation

A Test Program Subcommittee was appointed at the first Selection Committee meeting. This subcommittee proposed a set of 23 potential test programs, which were believed to be representative of the operations performed in military data processing applications. The Committee ranked these programs by their relative importance, and the top 12 programs were selected as the basis of the Test Program Experiment. These 12 programs are listed and briefly described in Table 3.

Each of the 12 test programs was a relatively small kernel-type program, most

were subroutines, and most were defined as "structured" programs in a Program Definition Language (PDL). Programmers were then asked to "hand compile" the programs into the assembly languages of the respective machines from their PDL descriptions. This procedure was followed to minimize the effects of programmer variations. No large scale programs from "real" military systems were coded, because of the excessive expense involved in coding and testing a statistically significant set of such programs. High level language programs were not tested, because there is no practical was to separate the effects of compiler efficiency from the effects of architecture efficiency which the experiment was intended to measure.

Slightly over one hundred test program samples were coded by 16 programmers at participating organizations. The experiment was designed using analysis of variance techniques to give the best possible estimates of the relative efficiency of the three architectures.

Three measures were defined to gauge the efficiency of the architectures, independently of hardware implementation features such as cycle time. These measures were:

- S The static storage requirement for the program in bits.

- M The number of bits of program and data which were transferred between the processor and main memory during execution of a program. The M Measure is intended to be an index of the memory bandwidth requirements of an architecture.

- R The number of bits of program and data which were transferred among the internal processor registers during execution of a program. The R Measure is intended to be an index of the processor bandwidth requirements of an architecture.

The S, M and R measures are indicators of the relative amounts of hardware capability that are necessary when implementing an architecture to do a certain job.

That is, larger S measure means that correspondingly more memory will be required to handle a given set of applications programs. Clearly, the architecture that can execute the programs with the smallest S is desirable. Similarly, M and R are indicators of the relative hardware speed/bandwidth requirements for memory and processor implementations.

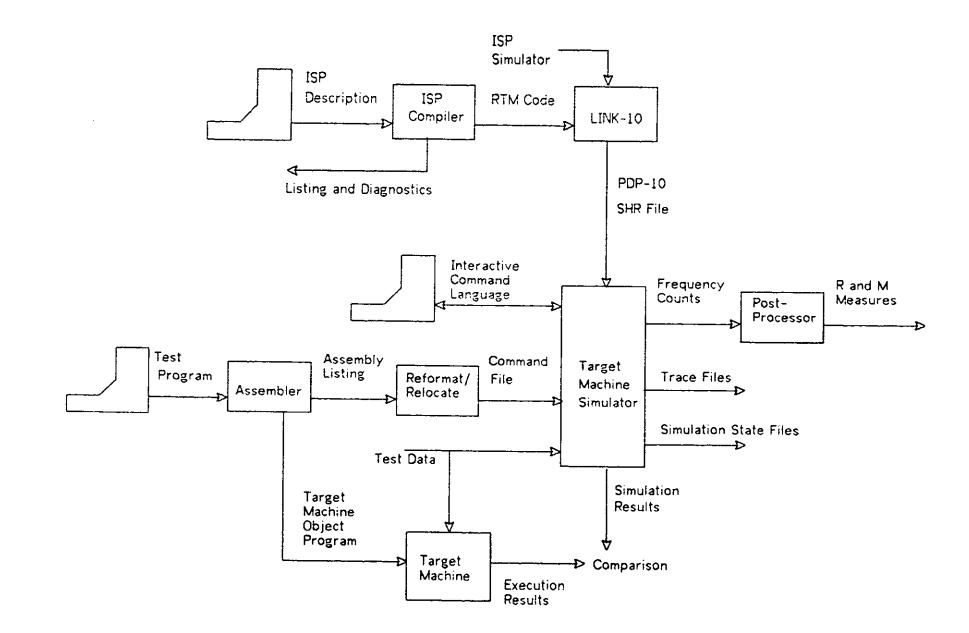

The S, M and R raw data were gathered with the help of a special ISP language compiler and simulator system. The three architectures were described in ISP (Instruction Set Processor), a formal language for describing computers at the instruction/register level. These ISP descriptions were then compiled and run on the ISP simulator which was designed to automatically gather statistics of register and memory activity during execution of the test programs on the simulated candidate architectures. See Volume IV of the Committee Report for a detailed treatment of the ISP System and its use in the CFA effort.

The final results reflect the performance of each candidate architecture for each measure. Those results are shown in Table 4. This experiment is described more fully in Volume III of the final Committee Report.

The results are normalized so that unity indicated average performance; the lower the score on any of the measures, the better the architecture handled the set of test programs. In other words, the results indicate that the S/370 needs 21 percent more memory than the average to store the test programs, the 8/32 needs only 83 percent as much memory as average, and the PDP-11 is nearly average in its use of memory. The differences between the S/370 results and the average of the results of the other two architectures were statistically significant at the 95 percent confidence level, but the differences between the 8/32 and the PDP-11 results were not

statistically significant at this confidence level. The differences between the 8/32 and the S/370 results were also statistically significant for the S and M measures at the 95 percent confidence level.

#### Support Software Evaluation

A support Software Evaluation Subcommittee was appointed to study the support software bases of the three final candidate architectures. This subcommittee began by defining an extensive menu of support software tools, which might be useful in military systems development. Committee member organizations were then asked to rate each tool by its utility in developing software for military weapon systems. The 28 most important support software tools were selected from this rating. The CFA candidate manufacturers and other commercial sources were investigated as to the availability of these 28 software tools for each architecture. Table 5 lists the basic tool types on the required support software menu.

The cost to develop each item of support software was estimated. The total cost to develop the selected support software items was estimated to be approximately 41 million dollars. The estimated value of the support software bases for each of the final candidate architectures is summarized in Table 6 below; also shown is the estimated cost to eliminate deficiencies as compaed to the desired support software base:

See Volume V of the Committee Report for a detailed treatment of the support software evaluation.

#### Life Cycle Cost Evaluations

A Final Selection Methodology Subcommittee was formed at the third Selection Committee meeting to investigate and pursue a methodology for combining the results

of the committee's evaluations into a single evaluation criterion which would be realistic and meaningful to DoD management. This subcommittee proposed a method of converting the architecture and software evaluation results to life cycle costs so that a final selection could be aided by data based on the comparative economics of using each of the candidate architectures in military computer systems.

Two separate computer life cycle requirements models were used for the cost analyses. Both used the data gathered in the Architecture Efficiency Evaluation and the Support Software Base Evaluation described previously to convert the modeled requirements into dollar costs.

The first model is a "top-down" model which represents total life cycle requirements for DoD computers in the 1978-1990 time period, using each of the three final candidate architectures for the MCF. It was based upon extrapolating trends in DoD wide expenditures and requirements for military computer hardware and software.

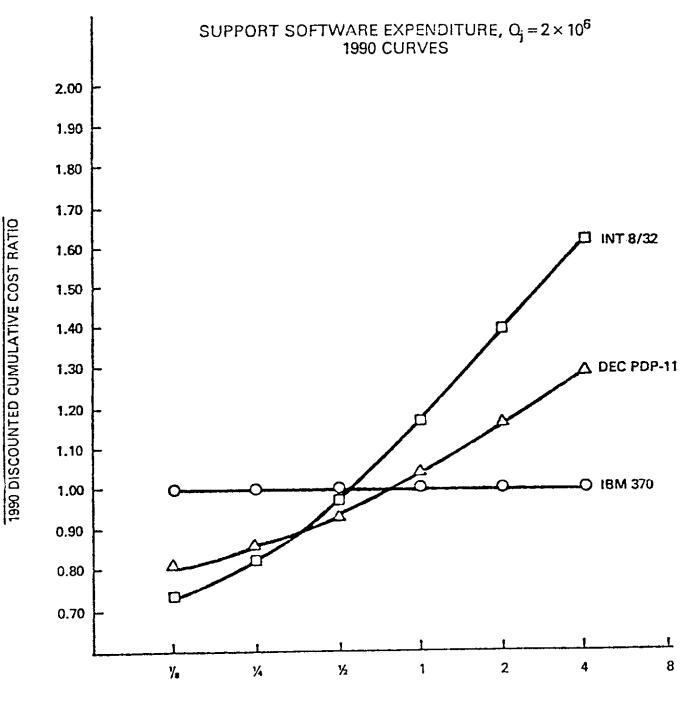

Figure 2 summarizes results of computing CFA life cycle costs summed over the years 1978 to 1990 for the three candidates, for certain conditions. To simplify comparisons, the total assumed costs (approximately \$1 billion) are normalized with respect to the IBM S/370.

The results are shown for specific values of two of the model input parameters. The first is an expenditure rate (\$2M/year) for completing development of the support software base of each candidate. The second is a range of values (x-axis) of the total cost ratio of software-to- hardware for military tactical computer systems. The results are plotted as a function of the software-hardware cost ratio because it is one of the most important parameters in the cost evaluations. Available data gives this ratio as about 2.5 to 3.0 for generalized ADP systems but less than that for tactical, embedded

computers where many copies of a single hardware and software design are deployed. How much less is not clear from available data. In the lower range of software/ hardware ratios the Interdata has the lowest cost, in the upper range the S/370 is lowest, and the PDP-11 is lowest in the middle range and neither best nor worst elsewhere.

The second model is a "bottom-up" life cycle requirements model, which is based upon data gathered on 15 existing or developmental Army tactical data systems. This model represented the life cycle requirements for these 15 systems, using each of the three final candidate architectures. The cost to develop all of these systems in 1976 and then in 1985 was estimated. The results of this analysis are shown in Table 7 below. This table indicates that:

- a. The average total life cycle cost for all 15 systems is estimated at \$1.91B in 1976 and \$250M in 1985. The average software: hardware cost ratio of these systems is 1:11 in 1976 and 1:2.3 in 1985.

- b. In 1976, the number of systems in which the PDP-11 architecture provides the lowest cycle cost is the largest (11). The PDP-11 architecture provides the lowest total life cycle cost by a small margin (3.7%) over the 8/32 architecture and by a larger margin (20.0%) over the S/370 architecture.

- c. In 1985, the number of systems in which the PDP-11 architecture provides the lowest cost increases to 14. The PDP-11 architecture continues to provide the lowest total life cycle cost for all 15 systems by margins of 8.8% and 17.6% over the 8/32 and \$/370 architectures.

Assumptions applicable to the results shown in Table 7 are (1) hardware cost reduction of a factor of 10 from 1976 to 1985, (2) hardware life cycle cost of twice the acquisition cost, and (3) software life cycle cost of 5.5 times the acquisition cost.

The results shown in Table 7 are not significantly sensitive to changes in applications software cost or in the annual support software investment for the selected CFA.

A limited sensitivity analysis was performed with both models. If lower estimates are made for software development costs (relative to hardware costs), and/or if faster development of the support software base is projected (so that all three architectures rapidly acquire a complete support software base), then the Interdata 8/32 eventually becomes the least expensive architecture, because of its efficient architecture as indicated by the test program results. If very high software development cost estimates are made, and/or very slow support software development is projected, then the S/370 becomes the least expensive architecture because of its advantage in support software. Figure 2 illustrates this behavior. In the intermediate ranges of software cost estimates, where top-down and bottom-up results were in the best agreement, the PDP-11 appears to have a slight cost advantage. However, compared to the expected errors in the results due to the uncertainties in the input data and assumptions, the life-cycle cost differences between the two models and among the three candidate architectures are small. The software/hardware ratio which is one of the most important factors in both models is one of the hardest to pin down with supporting data, and the results of both models can be made to change by using values from different sources for the same input parameters. The strongest conclusion to be derived is that the results agree and that, in terms of life cycle cost, all three candidates would provide comparable choices for the CFA. See Volume VI of the Final Report for details of the life-cycle cost evaluations.

#### Licensing

Meetings were held with IBM, DEC, and Interdata to discuss the terms and conditions under which they would grant a non-exclusive license to the Government to use their architecture for militarized processors. All three manufacturers were

cooperative and proposed terms for such an agreement. Although the proposed licensing agreements were a significant factor in the final selection process, the details cannot be given here, due to the confidential nature of the discussions. Volume VII of the Final Report, which is restricted to internal Government use, contains the details of the licensing proposals.

#### 6.3. Final Selection/Recommendations

The Selection Committee held its fifth and final meeting on 24 to 26 August 1976 at the Naval Underwater Systems Center, Newport, R. I., for the purpose of selecting the recommended aachitecture for the MCF. At this meeting, the results of the evaluations discussed in the preceding sections of this article were considered by the committee and discussed at length. Based upon that data, and upon other concerns specifically considered by the committee during its discussion of the final selection, the respective strengths and weaknesses of each architecture can be summarized as follows:

- A. INTERDATA 8/32. The 8/32 was the highest rated architecture on the Quantitative Criteria, and the Test Program Results. The 8/32 has a good interrupt structure for real-time processing. On the other hand, the software base is relatively weak, which consequently compromised its performance in the life cycle cost evaluations. There was a nagging question about how well the state of the machine was preserved after interrupts.

- B. IBM S/370. The strongest virtue of the S/370 is its large support software base. The S/370 performed well on the life-cycle cost analyses under assumptions of maximum relative cost of software development. The S/370 is the only architecture demonstrated as an easily virtualized computer in a standard product line. On the other hand, its interrupt structure was considered cumbersome for real time control applications. The test program results indicate that the architecture is significantly less efficient than the 8/32 and the PDP-11. There was also concern that small subset versions might not prove cost-effective for low-end applications, and that there was insufficient experience with the S/370 in OEM type applications.

C. PDP-11. The PDP-11 enjoys a good support software base, performed relatively well on the Test Programs, and has a good interrupt structure for real-time control applications. It enjoys a slight advantage on the cost models for a range of reasonable assumptions. Small scale (microprocessor) implementations are practical and have been built. On the negative side, the 16 bit virtual address space is a limitation and it may be expensive to add a virtual machine capability to the architecture.

The committee made four final recommendations:

- A. The DEC PDP-11 was determined by a vote of 14 to 4 to be the most advantageous architecture for the MCF, the IBM S/370 was ranked second, and the Interdata 8/32 was ranked third.

- B. The committee unanimously agreed that a single instruction-set architecture should be selected for the MCF, that the selection of only one architecture is more important than which one of the candidates is selected, and that any one of the three final candidate architectures could provide a satisfactory basis for the MCF.

- C. The committee agreed that an effort should be made to relieve the limitations of the selected architecture. In the case of the PDP-11 the major limitation is the small (16 bit) virtual address space.

- D. A single organizational structure must be established to control the architecture, or major incompatibilities between different implementations will surely result.

See Volume VIII of the Final Report for details of the CFA final selection/recommendation process.

### 7. Conclusions

It is sometimes asserted that military systems have unique requirements which preclude the use of a general purpose commercial instruction set. Developers of computer based weapons systems often assert that they alone have such severe "realtime" constraints that they compel the use of a particular processor. It is worth noting that the Selection Committee compared three of the most widely used military architectures with six of the most widely used commercial architectures and found that

the military architectures were deficient compared to the commercial architectures in terms of those architectural characteristics believed to be most important in tactical military applications. It is worth noting also that none of the military architectures had any unique features which proved advantageous, while all three were found to have architectural shortcomings. Moreover, the support software available for the three military architectures is relatively weak. Considering how easily modern microprogrammable processor hardware may be adapted to a given instruction-set architecture, there appears to be little reason to continue to use little-known or immature developments in future military computer systems.

The PDP-11 is one of the most successful architectures, in terms of user acceptance, in the history of the computer industry. It has been manufactured in the tens of thousands, and is widely used in almost every sort of OEM application. An extensive support software base exists for it, and DEC will continue to develop and support the architecture for the foreseeable future. It is clearly a satisfactory choice for the Military Computer Family. With the MCF intelligently defined and implemented, it will make available a family of militarized processors with excellent software development tools, and the capability to develop and maintain software on less expensive commercial equipment. This in turn will result in substantial cost and quality benefits in the application of computers to military systems.

### 8. Appendix

Table of Contents of The Final Report of the CFA Selection Committee

A-1 Volume I – Introduction

Volume I explains the background, rational and organization of the Computer Family Architecture effort and the Selection Committee.

A-2 Volume II - Selection of Candidate Architecture and Initial Screening

Volume II describes the initial candidate selection, and discusses architectural issues pertinent to CFA evaluation. The evaluation criteria applied to the architectural candidates for preliminary screening are described in detail, and the results of that evaluation are discussed.

A-3 Volume III - Evaluation of Computer Architectures via Test Programs

Volume III discusses the development of the measures used to gauge architectural efficiency and describes the test programs selected for the evaluation. The method of specifying the test programs and the structure of the programming experiment to minimize programmer effects are also discussed.

A-4 Volume IV - Architecture Research Facility: ISP Description, Simulation, Data Collection

Volume IV discusses the use of the ISP machine architecture description language in describing the candidate architectures. It describes the ISP interpreter facility and its application to simulation of the candidates and in gathering the measurements discussed in Volume III.

A-5 Volume V - Procedure for and Results of the Evaluation of the Software Bases of the Candidate Architectures for the Military Computer Family

Volume V describes a menu of support software tools determined to be important to the development of military software. It discusses how a subset of those tools were selected as the necessary software base for the Military Computer Family and the results of a study to determine the availability and value of these tools.

A-6 Volume VI - Life Cycle Cost Analyses of the Computer Family Architecture Candidates

Volume VI describes the methodology used to compute and compare

the life cycle costs of the CFA finalists and describes two life cycle models (top-down and bottom-up) and the results of applying the methodology to those two models.

A-7 Volume VII - CFA/Software Licensing Discussions with the Three CFA Finalists (For Official Use Only)

Volume VII addresses the technical, financial, and legal issues arising out of discussions with the owner/manufacturer of each candidate computer architecture and describes the outcome of these discussions.

A-8 Volume VIII - CFA Final Selection

Volume VIII discusses the consideration by the Selection Committee of the results of the architecture evaluations described in Volumes II through VII of this report. The influencessthat the various results had on the final selection are described.

A-9 Volume IX - A Consideration of Issues in the Selection of a Computer Family Architecture

Volume IX addresses questions and controversial issues regarding the CFA Selection process that arose from both within and without the Selection Committee during the course of the CFA effort.

FIGURE 1. CFA Selection Procedure

Table 1 - Absolute Criteria for CFA Evaluation

- (1) Virtual Memory Support.- The architecture must support a virtual to physical translation mechanism.

- (2) *Protection.-* The architecture must have the capability to add new, experimental (i.e., not fully debugged) programs that may include I/O without endangering reliable operaion of existing programs.

- (3) Floating Point Support.- The architecture must explicitly support one or more floating point data types with at least one of the formats yielding more than 10 decimal digits of significance in the mantissa.

- (4) Interrupts and Traps.- It must be possible to write a trap handler that is capable of executing a procedure to respond to any trap condition and then resume operation of the program. The architecture must be defined such that it is capable of resuming execution following any interrupt.

- (5) Subsetability.- At least the following components of an architecture must be able to be factored out of the full architecture:

Virtual-to-Physical Address Translation Mechanism

Floating Point Instructions and Registers (if separate from general purpose registers)

Decimal Instructions Set (if present in full architecture)

Protection Mechanism

- (6) Multiprocessor Support.- The architecture must allow for multiprocessor configurations. Specifically, it must support some form of "test-and- set" instruction to allow the implementation of synchronization functions such as P and V.

- (7)Controllability of I/O.- A processor must be able to exercise control over any I/O Processor and/or I/O Controller.

- (8)Extendibility.- The architecture must have some method for adding instructions to the architecture consistent with existing formats. There must be at least one undefined code point in the existing opcode space of the instruction formats.

- (9)Read Only Code.- The architecture must allow programs to be kept in a read-only section of primary memory.

### Table 1 (cont.) - Quantitative Criteria for CFA Evaluation

- (1) Virtual Address Space

- (a)  $V_1$ : The size of the virtual address space in bits.

- (b)  $V_2$ : Number of addressable units in the virtual address space.

- (2) Physical Address Space

- (a)  $P_1$ : The size of the physical address space in bits.

- (b)  $P_2$ : The number of addressable units in the physical address space.

- (3) Fraction of Instruction Space Unassigned

- (4) Size of Contral Processor State

- (a)  $C_s 2$ : The number of bits in the processor state of the full

(b)  $C_s 2$ : The number of bits in the processor state of the minimum subset of the architecture (i.e., without Floating Point, Decimal, Protection, or Address Translation Registers).

(c)  $C_m 1$ : The number of bits that must be transferred between the processor and primary memory to first save the processor state of the full architecture upon interruption and then restore the processor state prior to resumption.

(d)  $C_m^2$ : The measure analogous to  $C_m^1$  for the minimum subset of the architecture.

(5) Virtualizability

K: is unity if the architecture is virtualizable as defined in [PopG74] otherwise K is zero.

(6) Usage Base

(a)  $B_1$ : Number of computers delivered as of the latest date for which data exists prior to 1 June 1976.

(b) B<sub>2</sub>: Total dollar value of the installed computer base as of the latest date for which data exists prior to 1 June 1976.

(7) I/O Initiation

I: The minimum number of bits which must be transferred between main memory and any processor (central, or I/O) in order to output one 8-bit to a standard peripheral device.

## (8) Direct Instruction Addressability

D: The maximum number of bits of primary memory wwich one instruction can directly address given a single base register which may be used but not modified.

# (9) Maximum Interrupt Latency

Let L be the maximum number of bits which may need to be transferred between memory and any processor (CP, IOC, etc.) between the time an interrupt is requested and the time that the computer starts processing that interrupt (given that interrupts are enabled).

- .

-

# Table 2 - Candidate Scores on Absolute and Quantitative Criteria

| Architecture | Quantitative<br><u>Criteria Score</u> | Absolute<br>Criteria Score        |

|--------------|---------------------------------------|-----------------------------------|

|              |                                       |                                   |

| 8/32         | 1.68 (Best)                           | Problem with interrupts and traps |

| PDP-11       | 1.43                                  | Passed all                        |

| S/370        | 1.36                                  | Passed all                        |

| AN/GYK-12    | .94                                   | Failed floating-point             |

| ROLM/NOVA    | .92                                   | Failed virtual memory mapping and |

|              |                                       | interrupts/traps                  |

| B6700        | .91                                   | Failed protection                 |

| SEL-32       | .86                                   | Failed virtual memory mapping     |

| AN/UYK-7     | .46                                   | Failed floating point             |

| AN/UYK-20    | .44 (worst)                           | Failed protection                 |

# Table 3 - Test Programs

- 1. *I/O kernel, four priority levels,* requires the processor to field interrupts from four devices, each of which has its own priority level. While one device is being processed, interrupts from higher priority devices are allowed.

- 2. I/O kernal, FIFO processing, also fields interrupts from four devices, but without consideration of priority level. Instead, each interrupt causes a request for processing to be queued; requests are processed in FIFO order. While a request is being processed, interrupts from other devices are allowed.

- 3.  $I \neq 0$  device handler, processes application programs' requests for I/O block transfers on a typical tape drive, and returns the status of the transfer upon completion.

- 4. Large FFT, computes the fast Fourier transform of a large vector of 32 bit floating point numbers. This benchmark exercises the machine's floating point instructions, but principally tests its ability to manage a large address space.

- 5. Character search, searches a potentially large character string for the first occurrence of a potentially large argument string. It exercises the ability to move through character strings sequentially.

- 6. Bit test, set, or reset tests the initial value of a bit within a bit string, then optionally sets or resets the bit. It tests one kind of bit manipulation.

- 7. Runge-Kutta integration numerically integrates a simple differential equation using third-order Runge-Kutta integration. It tests floating-point arithmetic.

- 8. Linked list insertion inserts a new entry in a doubly-linked list. It tests pointer manipulation.

- 9. Quicksort sorts a potentially large vector of fixed-length strings using the Quicksort algorithm. Like FFT, it tests the ability to manipulate a large address space, but it also tests the ability of the machine to support recursive routines.

- 10. ASCII to floating point converts an ASCII string to a floating point number. It exercises character-to-numeric conversion.

- 11. Boolean matrix transpose transposes a square, tightly-packed bit matrix. It tests the ability to sequence through bit vectors by arbitrary increments.

- 12. Virtual memory space exchange changes the virtual memory mapping context of the processor.

-

•

-

# Table 4 - Test Program Experiment Results

| Architecture   | <u>s</u> | М    | <u>R</u> |

|----------------|----------|------|----------|

| Interdata 8/32 | .83      | .85  | .83      |

| PDP-11         | 1.00     | .93  | .94      |

| IBM S/370      | 1.21     | 1.27 | 1.29     |

#### Table 5 - Menu of Required Software Tool Types

Compilers Macro Assemblers Interactive Source Language Editors Interactive Symbolic Debuggers Extended Overlay Linker **Test Case Design Advisors** Integrated Library **Text Processing System** Data Base Management System **GP** System Simulator Time Sharing Operating System (TSOS) + VMM Language Independent Monitors **Test Data Generator** Non-Interactive Symbolic Debugger **Computer System Simulator** Batch Source Language Editors Language Dependent Monitors TSOS + MPOS + VMM Basic Assembler RTOS + TSOS Test Instrumenters & Analyzers Automatic SW Production & Test **Basic Linker** Standards Enforcers Reformatters Test Data Auditor Simple Overlay Linker Data Base Design Aid

-

-

# Table 6 - Tactical Support Software Base Evaluation

| Architecture | Estimated Value of<br>Current SSW Base | Estimated Cost<br>To Eliminate<br>Deficiency |

|--------------|----------------------------------------|----------------------------------------------|

| 8/32         | \$15.3 M                               | 825.9 M                                      |

| PDP-11       | \$22.2 M                               | 819.1 M                                      |

| S/370        | \$32.3 M                               | 8 9.6 M                                      |

SOFTWARE-TO-HARDWARE RATIO (2)

FIGURE 2. Top Down Life Cycle Cost Curves

# A. AVERAGE TOTAL LIFE CYCLE COSTS (\$000,000)

| Type Cost | 1976   | 1985  |

|-----------|--------|-------|

| Hardware  | \$1750 | \$175 |

| Software  | 162    |       |

| TOTAL     | \$1912 | \$250 |

# B. 1976 ARCHITECTURE COMPARISON

| Architecture | # System    | Relative Total Cost* |      |       |  |  |

|--------------|-------------|----------------------|------|-------|--|--|

|              | Preferences | HDW                  | SW   | Total |  |  |

| 8/32         | 1           | .92                  | 1.33 | .96   |  |  |

| PDP-11       | 11          | .91                  | 1.00 | .96   |  |  |

| S/370        | 3           | 1.16                 | .67  | 1.12  |  |  |

# C. 1985 ARCHITECTURE COMPARISON

| Architecture | # System    | Relat | 1 Cost* |       |

|--------------|-------------|-------|---------|-------|

|              | Preferences | HDW   | SW      | Total |

| 8/32         | -           | .92   | 1.20    | 1.00  |

| PDP-11       | 14.5        | .91   | .91     | .91   |

| S/370        | 0.5         | 1.16  | 1.09    | 1.09  |

\* with respect to average cost; 1.00 equals average cost

TABLE 7. Summary: Bottom Up Life Cycle Cost Analysis

# INITIAL SELECTION AND SCREENING OF THE CFA CANDIDATE COMPUTER ARCHITECTURES

-

Samuel H. Fuller, Carnegie-Mellon University and Naval Research Laboratory

Harold S. Stone, University of Massachusetts

and

William E. Burr US Army Electronics Command

•

-

# TABLE OF CONTENTS

# SECTION

# PAGE

| 1 | Intro   | duction                                              |

|---|---------|------------------------------------------------------|

| 2 | Initial | Selection of Candidate Computer Architectures        |

| 3 | Absol   | ute Criteria                                         |

| 4 | Quant   | itative Criteria                                     |

| 5 | Comp    | osite Score of the Quantitative Criteria             |

|   | 5.1     | Relative Weighing of Criteria                        |

|   | 5.2     | Normalization                                        |

|   | 5.3     | Scaling and Composition of the Quantitative Measures |

| 6 | Summ    | ary                                                  |

# ABSTRACT

The initial selection criteria that were developed and used by the Army/Navy Computer Family Architecture (CFA) committee in their evaluation of alternative computer architectures is presented in this article. These initial criteria were used in this first phase of the CFA evaluation process to reduce the number of computer architectures from the original set of nine to the most promising three or four architectures for the more intensive evaluation discussed elsewhere [FulS77; WagJ77; SmiW77]. The machines selected by this initial ranking and screening process for further evaluation were the Interdata 8/32, DEC PDP-11, and the IBM S/370.

# 1. Introduction

The CFA selection committee was concerned with selecting a computer architecture to use in future military (ruggedized) computers and hence wanted to evaluate the merits of the computer architecture independent of any features, or flaws, of existing implementations of the computer. For this reason, the following definition of computer architecture was used by the CFA committee:

> <u>Computer</u> <u>Architecture</u>: The structure of the computer a programmer needs to know in order to write any machinelanguage program that will run correctly on the computer.

With a well specified architecture, details of data bus width, technology (core memory versus semiconductor memory, TTL versus ECL circuits), implementation speedup techniques, physical size of computer, etc. need not be of concern to the programmer and hence are not a part of the architecture. This separation of architecture and implementation is not a radically new idea [AmdG64]. The IBM System/360-370 series, the DEC PDP-11 series, and the Data General NOVA series are

just three examples of where this has already been successfully accomplished to a greater or lesser degree.

This article first describes how the CFA selection committee chose the initial candidate architectures for evaluation, and then describes the criteria, the methodology, and the data used in ranking these architectures during the preliminary screening phase of the CFA project. At the point this procedure was formulated, it was known that time and money limitations would preclude doing a detailed analysis on all nine candidates; consequently an initial screening was necessary to limit the field to the three or four "best" candidates that would be subjected to a much more detailed analysis. This more detailed analysis, based on test programs, the support software bases of the architectures, and life cycle cost models is discussed in the accompanying articles.

Many detailed questions arose during the evaluation of these nine initial candidate architectures. It is impossible to review all these questions in this article, but we will discuss here the most important questions that arose, and interested readers are encouraged to refer to Volume II of the final report of the CFA committee for a detailed presentation of how and why each candidate architecture was evaluated as it was [FulS76a].

The mechanism for choosing the nine initial candidate architectures is discussed in the next section. The third and fourth sections then describe the nine absolute and seventeen quantitative criteria, respectively, and show how each of the candidate architectures was ranked on these criteria. The fifth section describes how the CFA committee combined the scores of the candidate architectures for each individual criteria to form a single, composite score for each architecture that reflected the relative importance of the seventeen quantitative criteria.

# 2. Initial Selection of Candidate Computer Architectures

The CFA selection process was initiated in March and April of 1975 when letters were sent to 35 Army and Navy organizations soliciting proposals for candidate computer architectures. As a result of these letters, and discussions at the first two CFA meetings, the following set of nine computer architectures was chosen:

| Burroughs 6700   | ROLM Corporation 1664 (AN/UYK-28) * |

|------------------|-------------------------------------|

| DEC PDP-11       | SEL 32                              |

| IBM System/370   | Univac AN/UYK-7                     |

| Interdata 8/32   | Univac AN/UYK-20                    |

| Litton AN/GYK-12 | •                                   |

There were on the order of 100 viable computer architectures in 1975 that might have been considered by the CFA committee for selection [GMLC75]. The decision as to what set of architectures would be evaluated remained open from March through December of 1975. The nine architectures listed above were selected for evaluation because they met two essential criteria: (1) the CFA committee agreed the architecture might be a reasonable choice for future military computers and (2) there was a CFA committee member sufficiently convinced of the value of the computer architecture that he was willing to act as its advocate in the subsequent evaluation phase.

#### 3. Absolute Criteria

The CFA selection committee specified nine <u>absolute criteria</u> that they felt a candidate computer architecture needs to satisfy if it is going to meet the

<sup>\*</sup> The AN/UYK-28 is instruction-set upward-compatible with the Data General NOVA computer architecture. Other ROLM computers that are also compatible with the NOVA architecture are the AN/UYK-19 and AN/UYK-27. The AN/UYK-28 is incompatible with the Data General ECLIPSE computer architecture, Data General's upward-compatible extension of the NOVA.

requirements of future military computer systems. All the absolute criteria (with the exception of the subsetability criterion) had to be satisfied by an implementation of the architecture which was operational by 1 January 1976. This eliminated speculative decisions based on promises or potential solutions that looked inviting, but might not come to fruition. Failure to satisfy any absolute criterion resulted in the elimination of the architecture from further consideration. The nine absolute criteria are given below. The formal statement of each criterion is underlined, while explanations and examples are not underlined. Many of the comments that follow the definition of an absolute criteria are the result of the experience gained when the CFA committee evaluated the nine candidate architectures against these criteria [StoH76]. Table 3-1 shows which absolute criteria each candidate architecture passed or failed.

# Virtual Memory Support.-The architecture must support a virtual to physical address translation mechanism.

The intent of this criterion is to take advantage of the widely used feature of many machines that is known as virtual memory. Many advantages accrue to architectures that support virtual address translation mechanisms, the most notable of which is the ability to simplify programming by freeing the programmer of explicit management of his primary memory and providing a mechanism for keeping only the active portions of a program in high-speed memory.

The answers for this criterion listed in Table 3-1 are not controversial, except for the AN/UYK-20. This architecture provides the page registers necessary for relocation, but does not limit the ability to change these registers to privileged programs. Some members of the CFA committee felt that preventing user state access to the page registers was a necessary aspect of virtual memory; others disagreed.

The full CFA committee voted to fail the AN/UYK-20 on this criteria. The ROLM 1664 and SEL 32 both failed this criterion because each of these architectures provide a mechanism commonly known as "bank switching", which the committee felt was not an adequate memory translation mechanism.

Protection.-The architecture must have the capability to add new, experimental (i.e., not fully debugged) programs that may include I/Q without endangering reliable operation of existing programs. The intent of this criterion is to provide a mechanism in the hardware for aiding software development, and for preventing certain catastrophic software failures from occurring in the field. Architectures that use a privileged mode to protect vital registers and system resources generally meet this criterion.

The AN/UYK-20 failed this criterion because it lacks memory protection; any user can modify the contents of the relocation registers, and thereby read and write any word in memory. Another generic way for an architecture to fail the protection criterion is for a program to have the ability to put the machine into a noninterruptable state for an indefinite time. Architectures that permitted nonterminating instructions were carefully examined to identify if these were, or were not, interruptable.

Floating-Point Support.-The architecture must explicitly support one or more floatingpoint data types with at least one of the formats yielding more than 10 decimal digits of significance in the mantissa. The significance measure was determined as representative of the most stringent requirements actually encountered.

The AN/GYK-12 failed this criterion because it does not support floating point

operations. The AN/UYK-7 failed because it supports a single, 64-bit floating point format with only 31 bits (9.2 decimal digits) of mantissa. Because this is so close to the borderline, one might reconsider requirements on significance to determine how firm the 10 decimal digit criterion is. (Had the AN/UYK-7 looked like an otherwise excellent architecture, it is likely that the committee would have relaxed the floating point absolute criterion for it.)

Interrupts and Traps.-It must be possible to write a trap handler that is capable of executing a procedure to respond to any trap condition and then resume operation of the program.

For example, if the processor receives a page-fault trap from the address translation unit, it must be able to request the appropriate page be brought in from secondary storage and then resume execution. If resumption of execution is logically impossible (e.g., an attempt to store an operand into a read-only segment of virtual memory or fetch an instruction with a parity error) then the trap handler should be able to abort the program with an indicator of which instruction and/or operand caused the termination.

A similar requirement exists for interrupts: <u>the architecture must</u> be <u>defined</u> <u>such that it is capable of resuming execution following any interrupt</u> (e.g., power failure, disk read error, console halt).

Another intent of this criterion is to permit extensions and subsets of an architecture to operate correctly so programs can be upward or downward compatible. The subsets and extensions may differ drastically in size, cost, and performance, but every program written for the native architecture can run on the subset or extended machine.

The Interdata 8/32 had difficulty satisfying this criterion since it has variable length instructions, and there is no way after a trap or an interrupt to tell whether the instruction which was being executed was a 16, 32, or 48 bit instruction. This may be a problem when it is desirable to correct the cause of the fault, and then re-execute (or resume) the instruction. Due to uncertainties in the definition of the Interdata 8/32 architecture, the CFA committee was not able to resolve whether or not the Interdata 8/32 satisfied this criterion.

Subsetability.-At least the following components of an architecture must be able to be factored out of the full architecture:

- a. Virtual-to-Physical Address Translation Mechanism

- b. Floating Point Instructions and Registers (if separate from general purpose registers)

- c. <u>Decimal Instructions Set (if present in full architecture)</u>

- d. <u>Protection Mechanism</u>

Implementations of the architectures on small machines for dedicated applications must not be required to include features of the architecture intended for use on larger, multiprogrammed, multi-application configurations. Existence of such subsets did not have to be demonstrated in an operational implementation of the architecture.

Because there was no operational method for testing subsetability, we could not challenge positive replies for any of the nine candidate architectures. However, the B-6700 and the AN/UYK-7 have not been subsetted in the sense of the criterion, so that their subsetability is more speculative.

In order to retain program compatibility across the implementations of the

architecture, this criterion was extended to include the following requirement: The trap mechanism of the architecture must be defined such that instructions in the full architecture, but not implemented in the subset machine, trap on the subset machine and that it be possible to write trap routines for the subset machine that allow it to interpretively execute those instructions not implemented directly in hardware (or firmware) and then resume execution. (This is an elaboration of absolute criterion 4.)

Multiprocessor Support.-The architecture must support some form of "test-and-set" instruction to allow for the communication and synchronization of multiple processors.

The intent of this criterion is to be sure that the basic architecture can support multiprocessor configurations.

# Input/Output Controllability.-A processor must be able to exercise absolute control over any I/O processor and/or I/O controller.

The interpretation of the criterion proved rather difficult. While all architectures necessarily permitted individual devices to be started and queried for status, there were varying degrees of control exercisable with respect to stopping the devices. It is reasonable to stop all input/output, or to stop selected devices. All architectures had some way of stopping a single device and stopping all devices, but how they did it varied widely in efficiency.

Extensibility.-The architecture must have some method for adding instructions to the architecture consistent with existing formats. There must be at least one undefined code point in the existing opcode space of the instruction formats. All nine candidate architectures have unused instructions, so all passed this criterion.

Read-Only Code.-It must be possible to execute programs from read-only storage.

This criterion is intended to permit an added degree of reliability by permitting programs to be stored in a nonvolatile read-only memory. However, a program can be rewritten to be read-only on any of the nine architectures, even if that architecture does not support special types of instructions to facilitate this. It might have been more meaningful to examine this question quantitatively.

Table 3-1 shows the score of each candidate architecture on each of the absolute criteria. Note that none of the nine architectures failed to meet the last five criteria: subsetability, multiprocessor support, I/O controllability, extensibility, and read-only code. This is in part the case because we limited our evaluation to reasonably successful architectures, but is partly the result of not defining these criteria precisely enough prior to applying them to the candidate architectures. For example, by not clearly defining how to test for the practical subsetability of an architecture, we made it virtually impossible for an architecture to fail this criteria. Subsequent studies would be well advised to consider more precise definitions of these (and any additional) absolute criteria before evaluating alternative architectures against them.

# 4. Quantitative Criteria

In addition to the absolute criteria, the CFA committee specified seventeen quantitative criteria that they felt would be helpful in the initial screening process. A number of these quantitative criteria measure attributes of a computer architecture better measured by benchmarks, or test programs [FulS77a]. However, the CFA committee recognized that it did not have the resources to run benchmarks on all nine candidate architectures and therefore proceeded with the use of these quantitative

criteria to help select three or four candidate architectures, out of the original nine candidate architectures, for more intensive study via test programs.

The quantitative criteria are described below and the score of each architecture on the quantitative criteria is given in Table 4-1.

#### Virtual Address Space.-

- V1: The size of the virtual address space in bits.

- V2: Number of addressable units in the virtual address space.

Two aspects of these measures were open to interpretation. The CFA committee settled on the following interpretation for treating bank switching: the virtual address for a machine with bank switching is the address within a bank. The effect of bank switching is to increase the size of the physical rather than the virtual address.

The second interpretation centered on the notion of "addressable unit". There are several degrees of addressability. An item may be fully addressable in the sense that it can be accessed by the address produced by an effective address computation. The committee also decided, however, that instructions such as the IBM S/370 Test Under mask, and the OR Immediate allowed the testing and setting of individual bits, and provided a minimum addressable unit of 1 bit.

# Physical Address Space.-

- P1: The size of the physical address space in bits.

- P2: The number of addressable units in the physical address space.

Where bank switching has been implemented, the physical address measures include all the banks of memory available. For computers with virtual address

translation, the physical address is the address resulting from the virtual-to-physical address translation. The physical address space is defined apart from any implementation, since the physical address space size is defined by the effective address calculation process or the virtual address translation process and need not be equal to the largest memory configuration yet delivered.

Fraction of Instruction Space Unassigned.-It is important to select an architecture that will allow reasonable growth over its expected lifetime. Let U be defined as the fraction of the instruction space in the architecture that is unassigned. Specifically:

$$U = \sum_{1 \le i \le \infty} u_j \cdot 2^{-i} \tag{4.1}$$

where ui is the number of unassigned instructions of length i.

Size of Central Processor State.-The amount of information that must be stored or loaded upon interrupt and/or context swapping is clearly an important factor in the response of real time systems and in the overhead of multiprogramming systems. Let the processor state be defined as all the bits of information in a processor that must be saved in order to be able to restart an interrupted process at a later date. Processor states normally include the accumulators, index registers, program counter, condition codes, memory mapping registers, interrupt mask registers, etc.

- C<sub>s1</sub>: The number of bits in the processor state of the full architecture.

- C<sub>s2</sub>: <u>The number of bits in the processor state of the minimum subset of</u> <u>the architecture</u> (i.e., without Floating Point, Decimal, Protection, or Address Translation Registers).

- C<sub>m1</sub>: <u>The number of bits that must be transferred between the processor</u> and primary memory to first save the processor state of the full architecture upon interruption and then restore the processor state prior to resumption. This measure differs from C<sub>s1</sub> above in that "register bank switching", where provided for in the candidate

architectures, may eliminate the need to save some registers in primary memory, while the instruction fetches required to save the state are included in  $C_{m1}$  but not in  $C_{s1}$ .

These measures give an approximation to the complexity of the implementation of the architectures, as well as a measure of the responsiveness of the architectures to worst-case context changes for interrupt processing.

If an architecture provides for several sets of certain registers to provide fast switching or multiple contexts, and if a program uses only one such register set when it runs in one context, then only one set of these registers is used in calculating  $C_{s1}$ .

Usage Base.-

- B1: <u>Number of computers delivered as of the latest date for which data</u> exists prior to 1 June 1976.

- B<sub>2</sub>: <u>Total dollar value of the installed computer base as of the latest date</u> for which data exists prior to 1 June 1976.

These two measures are meant to be approximate indicators of the existing software and programmer experience base. A single individual determined the value of these measures for all candidate architectures from standard sources.

# I/O Initiation.-

# I: <u>The minimum number of bits which must be transferred between main</u> <u>memory and any processor (central, or I/O) in order to output one 8-</u> <u>bit byte to a standard peripheral device.</u>

Although this measure was intended to give some insight into the responsiveness of an architecture, it is very difficult to construct an interpretation of the measure that serves this purpose well. The measure counts relatively few bits for some architectures, and this, in turn, makes the measure very sensitive to changes of a

few bits. The I measure is also sensitive to several assumptions about exactly what actions are to be performed in doing the input/output operation, and where parameters for the operation are found. Unfortunately, this sensitivity made the I measure very arbitrary, and a rather inexact measure of input/output responsiveness. The precise, and somewhat lengthy, definition of I is given in [FulS76a].

#### Virtualizability.-

# K: is unity if the architecture is virtualizable as defined in [PopG74], otherwise, K is zero.

The intent of this criterion is to capture the concept of virtual machines that has been used to advantage in some commercial computer systems (e.g., IBM's VM/370). An architecture that supports virtual machines provides a mechanism for a privileged, stand-alone program to run as an unprivileged task and produce the results identical to those it produces as a privileged program. The importance of this idea is that an operating system can be run in user mode as a subsystem of another operating system.

The definition of virtual machine as provide by Popek and Goldberg in their article in <u>CACM</u> [PopG74] is a very strict definition that guarantees that any operating system that can run stand-alone on architecture X, can also run on architecture X in nonprivileged mode. If an architecture fails this definition it may still support virtual machines in a more limited sense.

# Direct Instruction Addressability.-

D: <u>The maximum number of bits of primary memory which one</u> instruction can directly address given a single base register, which may be used but not modified.

Large displacement fields in instructions generally simplify programming because

they reduce the need to set base registers and to maintain addressability. Because an architecture may have several different instruction formats, each with different displacement field formats, the committee required that the format selected for this measure be the one used for standard LOAD and STORE operations, or the equivalent thereof. This eliminated anomalies, like the MOVE CHARACTER LONG in the IBM S/370 architecture, from consideration.

Maximum Interrupt Latency.-Let L be the maximum number of bits which may need to be transferred between memory and any processor (central processor, I/O controller, etc.) between the time an interrupt is requested and the time that the computer starts processing that interrupt (given that interrupts are enabled). This may be interpreted as a measure of the longest non-interruptable instruction or sequence of instructions. Architectures with nonterminating non-interruptable instructions have infinite L measures and are so indicated in Table 4-1.

### Subroutine Linkage.-

- J1: The number of bits which must be transferred between the processor and memory to save the user state, transfer to the called routine, restore the user state, and return to the calling routine, for the full architecture. No parameters are passed.

- J<sub>2</sub>: <u>The analogous measure to S1 above for the minimum architecture</u> (e.g., without Floating Point registers).

This measure gives an indication of the size of overhead that might be encountered in doing subroutine calls in the worst case for the biggest and smallest machines in the family. The bits counted here are related to the count in  $CS_1$ ,  $CS_2$ ,  $CM_1$ , and  $CM_2$ . By presumption, the bits that are stored for  $J_1$  are exactly those for  $CS_1$ , except that it is not necessary to save the protection registers, memory map

registers, interrupt mask, and other registers that determine the global context for a program. Architectures with small processor states or that have LOAD/STORE MULTIPLE instructions show up well on these measures.

#### 5. Composite Score of the Quantitative Criteria