# NOTICE WARNING CONCERNING COPYRIGHT RESTRICTIONS:

The copyright law of the United States (title 17, U.S. Code) governs the making of photocopies or other reproductions of copyrighted material. Any copying of this document without permission of its author may be prohibited by law.

# **Final Report on Supercomputer Research**

15 November 1983 to 31 May 1988

Ellen P. Douglas, Alan R. Houser, C. Roy Taylor, Editors

June 1989 CMU-CS-89-157

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

This research was sponsored by the Defense Advanced Research Projects Agency, DoD, through DARPA order 4864, and monitored by the Space and Naval Warfare Systems Command under contract N00039-85-C-0134. Views and conclusions contained in this document are those of the authors and should not be interpreted as representing official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or of the United States Government.

# Abstract

This report documents DARPA-supported supercomputer research in Carnegie Mellon University's Computer Science Department during the period 15 November 1983 through 30 September 1987, extended to 31 May 1988. Each chapter discusses one of four major research areas. Sections within each chapter present the area's general context, the specific problems addressed, our contributions and their significance, and an annotated bibliography.

The research areas and their main objectives are:

- SuperComputer Workbench [SCW]: Develop a multiprocessor operating system, programming environment, and instrumentation environment to support multiprocessor computing research.

- Systolic Array Machine [SAM]: Develop a powerful computational engine using systolic architectures and interconnections tailored to specific tasks.

- Production System Machine [PSM]: Explore the use of parallel architectures for production systems and develop a machine especially for production systems.

- Command Action Team [CAT]: Continue work on a knowledge-based expert system designed to assess and monitor threats to a carrier group.

-

•

.

.

# **Table of Contents**

ĩ

| 1. INTRODUCTION                                                         | 1-1        |

|-------------------------------------------------------------------------|------------|

| 1.1 Research scope                                                      | 1-1        |

| 1.2 The Research environment                                            | 1-1        |

| 2. SUPERCOMPUTER WORKBENCH                                              | 2-1        |

| 2.1 Challenges in Multiprocessor and Distributed Operating Sys-         | 2-1        |

| tem Research                                                            | 2-1        |

| 2.1.1 Previous multiprocessor operating systems                         | 2-1        |

| 2.1.2 The Accent distributed operating system                           | 2-2        |

| 2.2 A UNIX-Compatible Distributed Multiprocessor Operating Sys-         | 2-3        |

| tem                                                                     | 2-5        |

| 2.2.1 Mach system overview                                              | 2-3        |

| 2.2.2 Building-block abstractions                                       | 2-4        |

| 2.2.3 A portable virtual memory management system                       | 2-5        |

| 2.2.4 Interprocess communication                                        | 2-5        |

| 2.2.5 Integrating memory and communication                              | 2-6        |

| 2.2.6 Sharing memory                                                    | 2-8        |

| 2.2.7 Extending the kernel                                              | 2-9        |

| 2.3 A Multiprocessor Programming Environment                            | 2-9        |

| 2.3.1 Programming multiprocessors for performance                       | 2-9        |

| 2.3.2 A Programming and instrumentation environment<br>2.4 Bibliography | 2-10       |

| 3. SYSTOLIC ARRAY MACHINE                                               | 2-12       |

| 3.0.1 System components                                                 | 3-1        |

| 3.0.2 Chronology                                                        | 3-1        |

| 3.0.3 Evaluation                                                        | 3-3        |

| 3.1 Developing the Architecture                                         | 3-4        |

| 3.1.1 Powerful systolic cells                                           | 3-5        |

| 3.1.2 Systolic communication support                                    | 3-5        |

| 3.1.3 Inter-cell control coupling                                       | 3-6        |

| 3.1.4 Gaining programmability without sacrificing efficiency            | 3-7        |

| 3.1.3 An integrated, general-purpose host                               | 3-7<br>3-8 |

| 3.2 Software system                                                     | 3-9        |

| 3.2.1 Language design                                                   | 3-9        |

| 3.2.2 An optimizing compiler                                            | 3-10       |

| 3.2.3 Programming environment                                           | 3-11       |

| 3.2.4 Debugger                                                          | 3-11       |

| 3.3 Applications                                                        | 3-12       |

| 5.5.1 Application areas                                                 | 3-12       |

| 3.3.2 Program partitioning methods                                      | 3-13       |

| 3.4 bibliography                                                        | 3-14       |

| 4. THE PRODUCTION SYSTEM MACHINE PROJECT                                | 4-1        |

| 4.1 Introduction                                                        | 4-1        |

| 4.1.1 Sources of parallelism in production systems                      | 4-1        |

| 4.1.2 Research goals and considerations                                 | 4-2        |

| 4.2 Designing a Parallel Interpreter                                    | 4-3        |

| TABLE OF CONTENTS                                       | 111  |

|---------------------------------------------------------|------|

| 4.2.1 Evaluating opportunities for parallelism          | 4-3  |

| 4.2.2 Bounding parallel architecture alternatives       | 4-5  |

| 4.2.3 Building a preliminary system                     | 4-7  |

| 4.3 Parallel Interpreter Implementations                | 4-9  |

| 4.3.1 Testing the OPS5 parallel interpreter             | 4-10 |

| 4.3.2 Implementing a parallel Soar interpreter          | 4-11 |

| 4.4 Bibliography                                        | 4-15 |

| 5. THE CAT EXPERT SYSTEM PROJECT                        | 5-1  |

| 5.1 Developing the Internal System                      | 5-1  |

| 5.1.1 Structure and maintenance of CAT's knowledge base | 5-1  |

| 5.1.2 Improvement of inference net maintenance rules    | 5-2  |

| 5.1.3 Studying alternative data representations         |      |

.

-

| E 1 9 Chududo o alta mante a tra                           | V-2 |

|------------------------------------------------------------|-----|

| 5.1.3 Studying alternative data representations            | 5-5 |

| 5.2 Developing the External System                         |     |

| or beveloping the External System                          | 5-6 |

| 5.2.1 Developing the alert facility                        |     |

| 5.0.0 Developing the alore radiaty                         | 5-6 |

| 5.2.2 Developing an automatic knowledge acquisition system | 5-6 |

| 5.3 Developing System-Testing Tools                        |     |

| the Developing System-Testing Tools                        | 5-9 |

| 5.3.1 Developing demonstration scenarios                   |     |

| 5201 Friday                                                | 5-9 |

| 5.3.2 LEANCAT                                              | E 0 |

| 5.2.0 LEANOAT             | 5-9  |

|---------------------------|------|

| 5.3.2 LEANCAT             | 5-9  |

| 5.4 Cooperation with NOSC |      |

|                           | 5-10 |

| I. GLOSSARY               |      |

|                           | I-1  |

# **1. INTRODUCTION**

This report documents parallel processing research conducted by Carnegie Mellon University's Computer Science Department (CMU-CSD). The Information Processing Techniques Office of the Defense Advanced Research Projects Agency (DARPA) supported this work during the period 15 November 1983 through 30 September 1987, extended to 31 May 1988.

The remainder of this chapter describes our research scope and the CMU-CSD research environment. Chapters 2 through 5 then present in detail our four major research areas: the SuperComputer Workbench, the Systolic Array Machine, the Production System Machine, and the Command Action Team (CAT) project. Sections in each chapter present the area's general research context, the specific problems we addressed, our contributions and their significance, and an annotated bibliography.

The bibliographies present selected references that reflect the scope and significance of CMU's contributions to basic and applied computer science. Wherever possible, particularly for key reports, we have included abstracts. Also, publication dates serve as a reasonable indicator of progress in the various problem areas. CSD Technical Report dates exhibit the closest correlation with temporal progress and the report text frequently reappears later in the more accessible archival literature.

### 1.1 Research scope

We organize the research reported here under four major headings. These interrelated categories and their major objectives are:

- SuperComputer Workbench [SCW]: Develop a multiprocessor operating system, programming environment, and instrumentation environment to support multiprocessor computing research.

- Systolic Array Machine [SAM]: Develop a powerful computational engine using systolic architectures and interconnections tailored to specific tasks.

- *Production System Machine [PSM]*: Explore the use of parallel architectures for production systems and develop a machine especially for production systems.

- Command Action Team [CAT]: Continue work on a knowledge-based expert system designed to assess and monitor threats to a carrier group.

# **1.2 The Research environment**

Research in the CMU Computer Science environment tends to be organized around specific experimental systems aimed at particular objectives, e.g. the demonstration of a systolic array machine or the design and fabrication of a parallel interpreter. This report describes several such activities. Sometimes the creation and demonstration of a system is itself an appropriate scientific objective. At other times, some level of system performance constitutes the scientific goal. Thus our work tends to emphasize concept demonstration rather than system engineering. These research systems provide a convenient way to discuss and even to organize the projects at CMU-CSD. They are not always, however, ends in themselves.

A major strength of the Carnegie Mellon University environment lies in the synergy resulting from close cooperation and interdependence among varied research efforts, despite their diverse foci. For example, our basic research in image understanding, supported by DARPA under a separate contract, has an extraordinarily large appetite for computational cycles. Work in low-level vision and applied domains such as road following and obstacle avoidance have put the high computational throughput and novel architecture of the SAM project's Warp machine to good use. Likewise, the SAM project has benefitted from the close relationship with researchers who actually apply the Warp machine to real tasks. This inter-project collaboration significantly influenced Warp, from the conceptual level of program partitioning models to the pragmatic level of rapid feedback regarding performance criteria and bottlenecks.

We have no administrative structure that corresponds to our organization of effort. We consist simply of faculty, research scientists, and graduate students of the Computer Science Department, with the facilities support divided into an Engineering Laboratory and a Facilities Software Group. The rest of the organization is informal. This organizational style minimizes the barriers between efforts and promotes the kind of interactions and synergy reflected in the work distribution shown in Table 1-1. .

.

.

|                                                                                                   | Number of<br>Areas | Mach | Warp | PSM/cat |  |  |

|---------------------------------------------------------------------------------------------------|--------------------|------|------|---------|--|--|

| Roberto Bisian                                                                                    | i 2                | x    | ×    |         |  |  |

| Scott Fahlman                                                                                     | 2                  | x    |      | x       |  |  |

| Lanny Forgy                                                                                       | 1                  |      |      | x       |  |  |

| Thomas Gross                                                                                      | 1                  |      | ×    |         |  |  |

| Takeo Kanade                                                                                      | 2                  | ×    | ×    |         |  |  |

| H.T. Kung                                                                                         | 3                  | x    | •    | x       |  |  |

| John McDermo                                                                                      | ott 1              |      |      | x       |  |  |

| Allen Newell                                                                                      | 2                  | x    |      | •       |  |  |

| <b>Rick Rashid</b>                                                                                | 1                  | x    |      |         |  |  |

| Raj Reddy                                                                                         | 3                  | x    | x    | x       |  |  |

| Zary Segali                                                                                       | 1                  | x    |      |         |  |  |

| Albert Spector                                                                                    | 1                  | x    |      |         |  |  |

| Daniel Siewiore                                                                                   | ek 1               | •    |      |         |  |  |

| Howard Wactla                                                                                     | r 1                | •    |      |         |  |  |

| x = Active research in this area<br>◆ = Responsible for area<br>Faculty participating, total = 14 |                    |      |      |         |  |  |

| Figure 1-1. Distribution of faculty offert                                                        |                    |      |      |         |  |  |

Figure 1-1: Distribution of faculty effort

٠

#### INTRODUCTION

# 2. SUPERCOMPUTER WORKBENCH

Multiple-processor computer architectures have emerged as a viable response to the challenge of providing sufficient computing power for computationally-intensive applications. When such architectures were first developed, however, they typically suffered from inadequate software support. Early multiprocessor systems normally featured a poor or non-existent programming environment and an operating system that did not take full advantage of the hardware's multiple-processor resources.

The goal of the SuperComputer Workbench project has been to provide software support tools specifically designed for shared-memory, multiprocessor architectures. Our work has produced two such support tools:

- A distributed multiprocessor operating system (Mach)

- A host software development and instrumentation environment (PIE)

These tools support researchers in producing, evaluating, and using multiprocessor computing systems. The Mach operating system permits full utilization of multiprocessor resources, an efficient mechanism for sharing memory, and full UNIX compatibility. Developers can port Mach to a variety of different architectures, as it supports single multiprocessor hosts, distributed computer networks, and individual workstations. The PIE programming and instrumentation environment provides tools for writing and debugging efficient multiprocessor programs and for evaluating them for their ability to fully exploit the underlying hardware and software.

# 2.1 Challenges in Multiprocessor and Distributed Operating System Research

# 2.1.1 Previous multiprocessor operating systems

Before Mach, there had been several efforts in developing multiprocessor operating systems. However, each has suffered from limitations in functionality, performance, or usability. None has approached our goal of a general-purpose, multiprocessor, distributed operating system.

Previous multiprocessor operating systems have generally fallen into one of three categories:

- Simple operating systems providing minimal functionality —These systems, such as the Cosmic Cube and the Butterfly, do not address operating system issues directly. Typically, they provide only basic functions required to use the hardware. Users must often cross-compile programs on a different machine, then download to execute. Such systems make it possible to use the target machine, but their user environments are less than desirable.

- Uniprocessor operating systems with simple modifications for use in a multiprocessor environment—Numerous other multiprocessor operating sys-

tems represent modifications of pre-existing uniprocessor systems. VMS has been extended to run in a dual-processor configuration and several UNIX<sup>1</sup> versions have been modified to run on multiprocessors. These systems usually run in a master/slave configuration and are not realistically extensible to large multiprocessors.

Completely new operating systems typically designed to run on a specific type of multiprocessor—Where completely new multiprocessor operating systems have been built, they were frequently accompanied by inadequate user environments and were difficult to use. Intel's IMax operating system for the 432 exemplifies such a system.

During this contract period, we began to lay the foundations for a general-purpose, multiprocessor, software support environment that does not suffer the limitations common to earlier efforts. Our current Mach operating system, built on the experience of previous research efforts, forms the prototype nucleus of such an environment.

Our previous work produced Accent, a uniprocessor distributed operating system [Rashid 86a]. Mach was conceived as an Accent-like operating system that would provide multiprocessor functionality and complete UNIX compatibility. Mach was designed to better accommodate the kind of general purpose, shared-memory multiprocessors that appear destined to succeed traditional general purpose uniprocessor workstations and timesharing systems.

#### 2.1.2 The Accent distributed operating system

Accent was organized around the notion of a protected, message-based interprocess communication facility integrated with copy-on-write virtual-memory management. Access to all services and resources, including the process and memory management services of the operating system kernel itself, was provided through Accent's communication facility. This design allowed completely uniform access to resources throughout the network. It also provided that access to kernel-provided services was indistinguishable from access to process-provided resources (with the exception of the interprocess communication facility itself).

Accent went beyond demonstrating the feasibility of the message passing approach to building a distributed system. Experience with Accent showed that a message-based network operating system, properly designed, can compete with more traditional operating system organizations. The advantages of this approach are system extensibility, protection and network transparency.

While Accent demonstrated the feasibility of a network operating system, it represented only an early step toward our long-term goal of a distributed, portable, multiprocessor operating system. Accent was a distributed *uniprocessor* operating system.

<sup>&</sup>lt;sup>1</sup>UNIX is a trademark of AT&T Bell Laboratories.

It did not have the necessary process management facilities to take advantage of multiprocessor architectures. Accent was largely *architecture dependent*, running on a network of 150 PERQ workstations.<sup>2</sup> Portability to other architectures would have required extensive modifications to the Accent kernel. Finally, Accent's slow "UNIX compatibility" package was ineffective in absorbing the ever-burgeoning body of UNIX-developed software.

# 2.2 A UNIX-Compatible Distributed Multiprocessor Operating System

A major reason that Accent never achieved widespread acceptance was its lack of true UNIX compatibility. For Mach to survive, UNIX compatibility was essential. To insure UNIX compatibility, we evolved Mach directly from the 4.2 BSD UNIX kernel. As we developed Mach features, we replaced existing UNIX features with our Mach implementations. This strategy had several advantages. It allowed us to maintain a working kernel throughout the Mach development process. It simplified the debugging of new kernel features. It also allowed us to incorporate into Mach new UNIX features developed outside CMU, such as the 4.3 BSD UNIX distribution and MIT's X window manager.

Our Mach design combines several low-level kernel abstractions with unique approaches in virtual memory implementation and interprocess communication. After presenting an overview of the current Mach operating system, we will discuss the building-block abstractions that form the basis of the Mach kernel design. We will then discuss Mach's virtual memory and interprocess communication facilities, both separately and as they together provide such Mach features as copy-on-write message passing and flexible memory sharing.

### 2.2.1 Mach system overview

Mach currently runs on a variety of architectures, including the entire VAX family of uniprocessors and multiprocessors, the IBM RT PC, the Sun 3, the Encore MultiMax, and the Sequent Balance 21000. Mach provides key functionality for parallel system software development, including

- Ability to allocate and manage large, sparse virtual memories

- A parallel multiprocessor scheduler with the ability to spawn new control threads cheaply within an address space

- Mechanisms for flexible memory-sharing among multiprocessor tasks

- Support for fine granularity synchronization

- Transparent communication between tasks running on both tightly- and loosely-coupled processor nodes

Our long-term goal is to have user-state server programs that reside outside the Mach

<sup>&</sup>lt;sup>2</sup>PERQ is a trademark of PERQ System Corporation.

kernel perform traditional operating system functions. During this contract period, we set the foundation for such an implementation. Our approach results in increased modularity and protective isolation among unrelated operating system functions. It also provides for a natural function decomposition in a multiprocessor system.

### 2.2.2 Building-block abstractions

The primary purpose of the Mach kernel is to provide an execution environment for user tasks and an interprocess communication (IPC) facility that allows user tasks to share data and resources. Our kernel design provides a minimal system abstraction set, extended from Accent, that forms the basic building blocks for a distributed multiprocessor computing environment:

- A *message* is a typed collection of data objects and consists of a fixed size header and a variable length body. Messages may be any size and may contain typed pointers to data outside the contiguous portion of the message body.

- A port is a kernel-protected queue for messages. At any given time, the maximum length of a port is fixed, although that fixed length can be changed. Tasks refer to ports through port capabilities. There are three kinds of port capabilities: send access, receive access, and ownership. Tasks obtain capabilities to ports only by receiving such capabilities in messages.

- A *task* represents the basic resource allocation unit, comprising a paged address space and access to system resources. A task may contain a single thread or multiple threads executing in parallel.

- A *thread* is the basic unit of computation, executing within a task. Threads may send and receive messages according to their access rights. When creating a thread, the kernel also creates a port, the *thread port*, to represent the thread. Messages sent to a thread port can alter the associated thread's state.

- A *process* is a thread operating within a task context. A standard UNIX process is equivalent to a Mach task with a single control thread.

- A memory object is a kernel-managed data repository. Memory objects can be created, destroyed, read or written. Backing storage for a memory object is determined by its type: permanent disk, temporary disk, physical memory, or port. Permanent disk memory objects are used to manage files. Temporary disk objects are used to back newly created virtual storage on disk and to shadow copy-on-write data. Physical memory objects are used to manage devices that operate on physical memory. Port memory objects provide copy-on-reference network access to data and any other on-demand creation or control of information.

A thread executes in the context of exactly one task; however, any number of threads may execute within a single task. Theoretically, all threads execute in parallel. This ability to execute multiple threads simultaneously within a task is the key feature in Mach's multiprocessor capability. Our multiprocessor scheduler and parallel thread execution capabilities allow Mach to take full advantage of the computing capacity of multiprocessor architectures.

The Mach kernel can be viewed as a task with its own 2<sup>32</sup> byte paged virtual address space and port access rights. The Mach network operating system is implemented as a collection of tasks running above the Mach kernel using the Mach IPC facility to communicate. Port capabilities are used to represent task-provided services, resources and data structures. As such, port capabilities serve a role in Mach similar to object capabilities in systems such as Hydra or StarOS. Interprocess interfaces in Mach are defined using MatchMaker, an object-oriented interface definition language developed for Accent [Jones and Rashid 86]. These interfaces are compiled into remote procedure call (RPC) stubs that use the Mach message passing primitives for communication and control.

# 2.2.3 A portable virtual memory management system

Proliferating hardware memory structures, with their varying requirements for virtual memory management, have hindered operating system portability. UNIX systems traditionally address the problem of virtual memory management portability by restricting the facilities provided and basing implementations for new memory management architectures on versions already done for previous systems. As a result, existing versions of UNIX, such as Berkeley 4.3 BSD, offer little in the way of virtual memory management other than simple paging support. Versions of Berkely UNIX on non-VAX hardware, such as SunOS on the Sun 3 and ACIS 4.2 on the IBM RT PC, actually simulate internally the VAX memory management specification.

Our goal was to implement a memory management system that would be readily portable to multiprocessor computing engines as well as to traditional uniprocessors. We designed our system by dividing Mach's virtual memory management code into machine *dependent* and machine *independent* sections [Rashid et al. 87]. Machine dependent code implements only those operations necessary to create, update and manage the hardware required for data structure mapping. All important virtual memory information is maintained by machine independent code. By clearly defining and organizing the machine dependent portion of the kernel, we greatly decrease the amount of time and effort required to port Mach to other architectures.

### 2.2.4 Interprocess communication

UNIX interprocess communication has never been flexible enough to easily build distributed systems. While advanced versions of UNIX, such as 4.3 BSD, continue to add communication mechanisms, the problems that distributed systems must address are glossed over. For example, internet domain sockets use a global machine-specific naming convention based on IP address, with a lack of location-independence and protection. To address the problems associated with building distributed systems, we designed Mach to provide a flexible interprocess communication facility through:

- A capability-based interprocess communication paradigm

- Typed message data

- Transparent extension of local communication into a network through message servers

- An interface language, Matchmaker, that generates client/server interfaces

- Integration with virtual memory management for 'efficient transfer of large messages

The Mach kernel itself has no knowledge of networks. The kernel doesn't have to distinguish between messages passed between tasks on the same host and messages passed over a network. Network message servers transparently extend communication over a network. A message sent to a port on a remote machine actually is sent to a network server on the sending host which then forwards the message over the network. The forwarding operation is transparent (and undetectible) to both the sender and the receiver.

In addition to simply extending the IPC paradigm to the network, network servers may participate in data type conversion and provide secure network transmission. By providing this functionality outside the kernel, Mach allows a host more flexibility in choosing data type representations, the amount or type of security to be used on a network and even the protocols to use for network transmission.

Matchmaker, our interprocess specification language, handles details of interprocess communication between different machine architectures and languages [Jones and Rashid 86]. Developed for Accent, Matchmaker enables a program to specify an interface between a client and server. Matchmaker allows a programmer to create a distributed program without worrying about the details of sending messages or type conversion between different machines.

Finally, the IPC mechanism makes use of the virtual memory system to make virtual, rather than physical, copies of large messages. This mechanism allows large amounts of data to be sent copy-on-write. Data is not copied from its original location unless a task writes to it. Our IPC facility is an especially important feature since a task usually only reads data, making data copying unnecessary.

#### 2.2.5 Integrating memory and communication

Mach combines virtual memory management and interprocess communication so that data may be transferred by memory mapping rather than data copying. Initially employed by Accent, by-value data transfer semantics are obtained by transferring message data with copy-on-write memory mapping, allowing multiple processes to access the same area of memory. Memory is not physically copied unless a process attempts to write to that memory space. Copy-on-write memory mapping saves the computational expense of making a physical copy of a memory region every time that region is accessed.

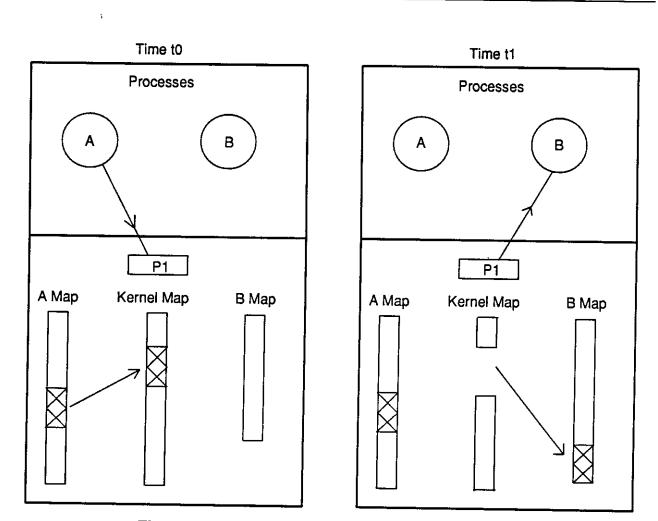

Figure 2-1 details schematically a copy-on-write data transfer between two Mach processes. At time *t0* process *A* sends a message containing a large amount of data (for example, an eight Mbyte pixel array gathered by a video camera) to communication port *P1*. When *A* sends the message, Mach marks corresponding memory areas in the address spaces of both *A* and the kernel (indicated by cross-hatched areas in their memory maps) "copy-on-write". At time *t1*, process *B* retrieves the message and Mach then moves the image data, again copy-on-write, into *B*'s address space. At no time is the data actually copied during these operations. A page-by-page copy would be performed only if *A* or *B* attempted to change parts of the transferred image.

Figure 2-1: Transferring data copy-on-write in Mach

By using copy-on-write mapping to transfer large data objects, Mach provides:

- Ability to transfer data objects in their natural size, up to and including the size of a process address space (as much as 2<sup>31</sup> bytes), unhindered by artificial message size limits

- Simple, mapped access to data such as files by making data objects directly addressable as regions of process address space, as in traditional P-MAP style file mapping

- Better utilization of both physical memory and backing storage through greater sharing between processes.

In addition to the ease of sharing memory, the integration of interprocess communication and virtual memory management provides another key Mach feature. Passing data by value in messages, Mach gains the advantages of simple communication semantics, including the ability to transparently extend communication in a large multiprocessor or onto a network with an absence of unintended side effects.

### 2.2.6 Sharing memory

Mach's memory sharing, through the copy-on-write message sharing provided by the IPC facility, works well for communicating tasks that require the protection of by-value message passing. It is also appropriate for applications with components intended for distribution over a local area network or loosely-coupled multiprocessor. On large, shared-memory multiprocessors, however, Mach provides two ways that processes can communicate more directly and efficiently:

- Many threads may directly share a single task address space

- A task may specify regions of its virtual address space as read/write inheritable to tasks it creates.

The ability to share memory between tasks allows for the sharing of global data structures at a page (4-8 Kbyte) level without incurring large performance penalties. It also provides access to the parallelism of memory access between tasks that require separate protection domains for other reasons. By including constructs for message passing, structured memory sharing between tasks and unrestricted sharing between threads, Mach can accommodate a range of multiprocessor architectures from looselycoupled multiprocessors and networks to tightly-coupled machines with low latency memory access.

Associated with each region of memory in a task's address space are a *current* and *maximum* protection. The current protection specifies what rights a task has to that memory in the form of a combination of read, write, and execute rights. The maximum protection describes the greatest set of protection rights a task may have. When a region of memory is allocated, a task has a maximum and current protection allowing all privileges. A task's current protection rights may be changed up to those specified by its maximum protection, or its maximum protection rights may be decreased. Separating maximum protection from current protection enables a parent task to provide protected (e.g. read-only) access to a portion of its memory.

### 2.2.7 Extending the kernel

Mach forms a single-machine operating system kernel, with all of its operations executing on a single processor or a single, shared-memory multiprocessor. The kernel's IPC facility, for example, supports only communication between tasks on the same machine. Our strategy for extending Mach to serve as a network operating system kernel was to design its abstractions, IPC facility, and virtual memory support to be transparently extensible by user-state tasks. This strategy permits server tasks, which are typically easier to prototype and develop than an operating system kernel, to provide traditional operating system functions.

Several examples illustrate the flexibility of Mach's primitives in providing traditional operating system functions. Rather than provide kernel support for network communication, we have implemented network server tasks that transparently extend Mach's IPC facilities between machines. We have developed an experimental file system that relies only on the kernel's memory object facilities for support. A file server task builds user file abstractions, such as directories, on top of the memory object. The file system server also uses network-transparent IPC to cooperate with other file servers in providing network-transparent remote file access. Finally, CMU's Camelot distributed transaction processing system is based on Mach's network interprocess communication facilities.

# 2.3 A Multiprocessor Programming Environment

# 2.3.1 Programming multiprocessors for performance

Historically, programming a parallel processor application has required a detailed knowledge of multiprocessor architecture and operating systems. The programmer had only rudimentary tools for creating parallel applications. Moreover, creating a correct parallel program has not been the end of the task. Often the only reason for developing a parallel program is for real-time performance. The difficult task of performance debugging and interpreting feedback in the context of a rudimentary program environment required an even more specialized and highly knowledgeable programmer.

A key element in a parallel debugging environment is an ability to collect data, through instrumentation support, on both the parallel hardware utilization (e.g., caches, buses, memories) and on system and application software performance (e.g., scheduling, resource management, virtual memory). In previous parallel programming research, such as the Cm<sup>+</sup> project, we found extensive instrumentation support critical to both the programming itself and to producing reliable, supportable, and maintainable software. There are two important reasons to integrate instrumentation with a parallel programming environment:

In a distributed parallel system, it is absolutely essential to assure target performance levels. System developers therefore need a programming environment that can support them in making performance-related decisions regarding program structure. Such support involves obtaining estimated performance data at program development time. An environment that provides this capability to program for performance must build on an instrumented base, that is, on a highly observable virtual machine (hardware+OS).

• Debugging a distributed or parallel program is far more complex than debugging a sequential program. The parallel application developer faces numerous hurdles, including a need to comprehend in detail the multiprocessor architecture and operating system, as well as a need to manually map intricate parallel algorithms onto parallel machines.

During the contract period we developed hardware instrumentation facilities for shared-bus, shared-memory multiprocessors, such as the Encore MultiMax and Sequent Balance. The facilities include several special-purpose hardware monitors under program control. These mechanisms provide the hardware monitoring basis for PIE, our Programming and Instrumentation Environment, and allow us to improve parallel program performance through detailed analysis of their CPU, cache, bus, and memory requirements.

### 2.3.2 A Programming and instrumentation environment

Our research in generating efficient parallel programs emphasizes two strategies, both embodied in our programming and instrumentation environment. The first approach involves avoiding performance bottlenecks through combining a coding methodology and performance prediction models to detect potential problems before undertaking extensive coding. The second approach, performance debugging, applies the concept of programming-for-observability.

During the contract period we continued to develop a programming and instrumentation environment (PIE) specifically tailored to parallel programming needs [Segall and Rudolph 85]. Our environment includes tools for constructing, instrumenting, and measuring parallel programs. PIE comprises a multilevel program development environment that assists the user in organizing, writing, and managing efficient parallel software and a tool set geared toward instrumenting such software for performance debugging.

The PIE environment consists of the following set of tools:

- MPC—a multiprocessor C language: MPC is a C preprocessor that converts special language constructs into C program systems. MPC resolves data consistency problems and handles physical synchronization and communication demands of multiprocessor code.

- PIEMACS is a syntax and semantics-based editor that automatically extracts the development time data about the target program and assists in instrumenting it for the run-time monitoring process.

- PIEMON (the PIE monitor) supports collection and storage of run-time event data via hardware instrumentation sensors.

#### SUPERCOMPUTER WORKBENCH

- PIEMAN (PIE manager) is a relational database which intelligently integrates development-time with run-time information.

- PIESCOPE is a graphical user interface which allows the programmer to view the development and execution of an MPC program.

PIE addresses the issues of performance debugging and programming for observability. The PIE environment tools aid the parallel programmer in both generating efficient multiprocessor programs and observing the execution of those programs for debugging and improvement of program efficiency. Additionally, PIE allows the programmer to write parallel programs without having to worry about the details of low-level process synchronization and communication. The PIE environment is designed to take the burden of these details off the user. The user can then concentrate on algorithm design and implementation to a greater degree than previously possible.

### 2.4 Bibliography

[Baron et al. 85] Baron, R., R. Rashid, E. Siegel, A. Tevanian, and M. Young. Mach 1: an operating system environment for large scale multiprocessor applications. *IEEE Software Special Issue*, July, 1985.

[Fitzgerald and Rashid 85]

Fitzgerald, R. and R. Rashid.

The integration of virtual memory management and interprocess communication in Accent.

Technical Report CMU-CSD-85-164, Computer Science Department, Carnegie Mellon University,

September, 1985.

The integration of virtual memory management and interprocess communication in the Accent network operating system kernel is examined. The design and implementation of the Accent memory management system is discussed and its performance, both on a series of message-oriented benchmarks and in normal operation, is analyzed in detail.

[Gregoretti and Segall 86]

Gregoretti, F. and Z. Segall.

Programming for observability support in a parallel programming environment.

In 14th Annual Computer Science Conference, ACM, February,

1986.

for observability concept for The programming performance/correctness debugging in a parallel programming environment is introduced. The design, first implementation, and evaluation of the required language and system support is presented. A two dimensional, multilevel, integrated monitoring system is described. Distinction is made between the monitoring mechanism, monitorand their implementation tradeoffs. policies ing PIEMON-1, an initial implementation of the presented design is outlined and evaluated.

[Jones and Rashid 86]

Jones, M. and R. Rashid.

Mach and Matchmaker: kernel and language support for objectoriented distributed systems

In 1st Annual OOPSLA Conference, ACM, October, 1986.

Mach, a multiprocessor operating system kernel providing capability-based interprocess communication, and Matchmaker, a language for specifying and automating the generation of multi-lingual interprocess communication interfaces, are presented. Their usage together providing a heterogeneous, distributed, object-oriented programming environment is described. Performance and usage statistics are presented. Comparisons are made between the Mach/Matchmaker environment and other systems. Possible future directions are examined.

[Rashid 86a]

Rashid, R.

From RIG to Accent to Mach: the evolution of a network operating system.

In Proceedings of the Fall Joint Computer Conference, ACM/IEEE, November, 1986.

This paper describes experiences gained during the design, implementation and use of the CMU Accent Network Operating System, its predecessor, the University of Rochester RIG system and its successor CMU's Mach multiprocessor operating system. It outlines the major design decisions on which the Accent kernel was based, how those decisions evolved from the RIG experiences and how they had to be modified to properly handle general purpose multiprocessors in Mach. Also discussed are some of the major issues in the implementation of message-based systems, the usage patterns observed with Accent over a three year period of extensive use at CMU and a timing analysis of various Accent functions.

#### [Rashid 86b]

Rashid, R.

Threads of a new system.

Unix Review 4(8):37-49, 1986.

The Department of Defense, anxious for better multithreaded application support, has funded the development of Mach, a multiprocessor operating system for UNIX applications.

[Rashid et al. 87] Rashid, R.F., A. Tevanian, M. Young, D. Golub, R. Baron, D. Black, W. Bolosky, and J. Chew.

Machine independent virtual memory management for paged uniprocessor and multiprocessor architectures.

In Proceedings of the Conference on Architectural Support for Programming Languages and Operating Systems, ACM, February, 1987.

Also appeared as tech-report CMU-CSD-87-140.

This paper describes the design and implementation of virtual memory management within the CMU Mach Operating System and the experiences gained by the Mach kernel group in porting that system to a variety of architectures. As of this writing, Mach runs on more than half a dozen uniprocessors and multiprocessors including the VAX family of uniprocessors and multiprocessors, the IBM RT PC, the SUN 3, the Encore Multimax, the Sequent Balance 21000 and several experimental computers. Although these systems vary considerably in the kind of hardware support for memory management they provide, the machine-dependent portion of Mach virtual memory consists of a single code module and its related header file. This separation of software memory management from hardware support has been accomplished without sacrificing system performance. In addition to improving portability, it makes possible a relatively unbiased examination of the pros and cons of various hardware memory management schemes, especially as they apply to the support of multiprocessors.

[Segall and Rudolph 85]

Segall, Z. and L. Rudolph.

PIE- a programming and instrumentation environment for parallel processing.

Technical Report CMU-CSD-85-128, Computer Science Department, Carnegie Mellon University,

April, 1985.

The issues of efficient development of performance efficient parallel programs is explored. Programming and Instrumentation Environment (PIE) for Parallel Processing system's concepts, designs, and preliminary implementation results are presented. The key goal in PIE is semiautomatic generation of performance efficient parallel In PIE, a system intensive rather that a programs. programmer intensive programming environment is promoted for supporting users with different experience in parallel programming. Three levels of such support are provided, namely the Modular Programming Metalanguage, the Program Constructor, and the Implementation Assistant. In order to facilitate the task of parallel programming, each component employs a set of new concepts and approaches to integrate functionality with performance concerns. This paper presents the results of PIE 1, the first of a three phase project.

[Tevanian and Rashid 87]

Tevanian Jr., A. and R.F. Rashid.

Mach: A basis for future UNIX development.

Technical Report CMU-CS-87-139, Computer Science Department, Carnegie Mellon University,

June, 1987.

Computing in the future will be supported by distributed computing environments. These environments will consist of a wide range of hardware architectures in both the uniprocessor and multiprocessor domain. This paper discusses Mach, an operating system under development at Carnegie Mellon University, that has been designed with the intent to integrate both distributed and multiprocessor functionality. In addition, Mach provides the foundation upon which future UNIX development may take place in these new environments. [Tevanian et al. 87a]

Tevanian Jr., A., R. Rashid, M.W. Young, D.B. Golub, M.R. Thompson, W. Bolosky, and R. Sanzi.

A Unix interface for shared memory and memory mapped filed under Mach.

In Proceedings of the Summer USENIX Technical Exhibition, USENIX, June, 1987.

This paper describes an approach to UNIX shared memory and memory mapped files currently in use at CMU under the Mach operating system. It describes the rationale for Mach's memory sharing and file mapping primitives as well as their impact on other system components and on overall performance.

[Tevanian et al. 87b]

Tevanian Jr., A., R.F. Rashid, D.B. Golub, D.L. Black, E. Cooper, and M.W. Young.

Mach threads and the Unix Kernel: the battle for control. In *Proceedings of the Summer USENIX Technical Exhibition*, USENIX, June, 1987.

This paper examines a kernel implemented lightweight process mechanism built for the Mach operating system. The pros and cons of such a mechanism are discussed along with the problems encountered during its implementation.

[Young et al. 87] Young, M., A. Tevanian, R. Rashid, D. Golub, J. Eppinger, J. Chew, W. Bolosky, D. Black, and R. Baron.

The duality of memory and communication in the implementation of a multiprocessor operating system.

In Proceedings of the 11th Symposium on Operating System Principles, ACM, November, 1987.

Mach is a multiprocessor operating system being implemented at Carnegie Mellon University. An important component of the Mach design is the use of memory objects which can be managed either by the kernel or by user programs through a message interface. This feature allows applications such as transaction management systems to participate in decisions regarding secondary storage management and page replacement.

This paper explores the goals, design and implementation of Mach and its external memory management facility. The relationship between memory and communication in Mach is examined as it relates to overall performance, applicability of Mach to new multiprocessor architectures, and the structure of application programs.

\_

•

# **3. SYSTOLIC ARRAY MACHINE**

Our objective in the Systolic Array Machine (SAM) project has been to demonstrate that we can build a useful supercomputer within both a short time period and a modest budget. In meeting this goal, we have developed the Warp machine [Annaratone et al. 87a]. Warp incorporates a systolic array of powerful, programmable cells, each capable of a 10 MFLOPS peak computing rate. In a typical configuration, the array comprises ten cells, thus offering a 100 MFLOPS aggregate computational bandwidth.

Warp's effectiveness results from a synergetic research strategy that simultaneously considers architecture, software, and applications. The Warp array's simple, linear topology supports several useful program partitioning models. In addition, each cell is highly programmable and has a large local memory. Together these features eliminate a need for the higher-dimensional connections that simpler systolic processors must employ to achieve equivalent power. With powerful cells, we need fewer of them to realize our performance goal. Warp complements its high cellular computation rate with correspondingly fast communication. The array's design provides high inter-cell bandwidths, while the host system provides high-speed external I/O. To deliver Warp's power into the programmer's hands, we developed a high-level language (W2) that provides detailed control down to cell-level parallelism, and an optimizing compiler that maps programs directly from W2 code to efficient machine instructions. Finally, we have facilitated user access to Warp's power by integrating the machine within UNIX as an attached processor, implementing a sizable application library that supports vision systems research, and developing general methods for mapping application problems onto the Warp array.

Our research has demonstrated the practicality of designing and building versatile, high-performance, systolic array computers. Warp's powerful array cells, fast communication, and user-accessible parallelism have extended its application domain substantially beyond that of previous designs. Programmability requires merely a physically larger machine and, given appropriate architectural support, does not degrade performance. We have, in fact, programmed Warp to execute well-known systolic algorithms---including matrix multiplication and convolution---as fast as special-purpose arrays employing comparable technology. Warp has also demonstrated high performance in diverse application areas, including low-level vision, signal processing, and scientific computing. As currently produced by our industrial partner, General Electric Corporation, Warp provides considerably more power and programmability than other machines of comparable cost.

### 3.0.1 System components

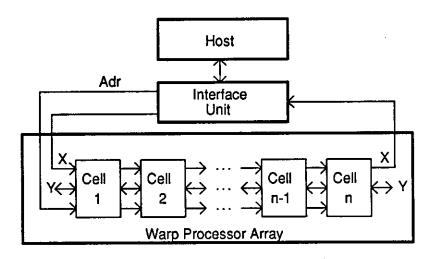

The Warp system, illustrated in Figure 3-1, has three major subsystems: processor array, interface unit, and host. The processor array performs the computation-intensive routines such as low-level vision routines or matrix operations. The interface unit (IU) handles input/output between array and host, and can generate memory addresses and control signals for the array. The host supplies data to and receives results from the

array. In addition, it executes those parts of the application programs that are not mapped onto the Warp array.

Figure 3-1: Warp system overview

The processor array is a linear systolic structure of identical Warp cells. Data flow through the cells on two communication channels (X and Y), and each cell's I/O bandwidth totals 20 Mword/s. The Y channel's direction is statically configurable, thus allowing bidirectional data flow. IU-generated control signals and local memory addresses propagate down the Adr channel.

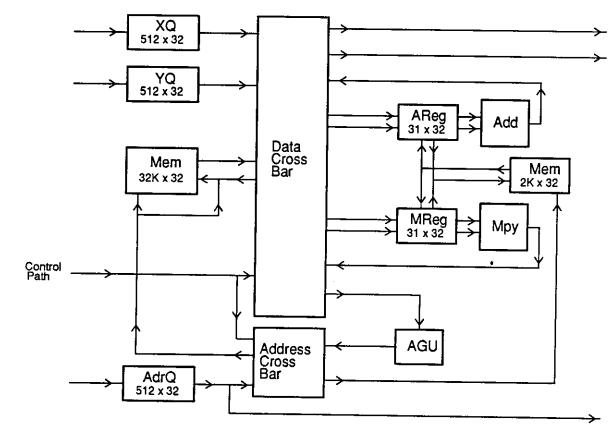

Each cell is implemented as a programmable, horizontal micro-engine, with its own microsequencer and program memory for 8K 272-bit instructions. The cell data path, shown in Figure 3-2, includes a 32-bit floating-point multiplier (Mpy), a 32-bit floating-point adder (Add), two local memory banks for resident and temporary data (Mem), a queue for each inter-cell communication channel (XQ, YQ, and AdrQ), and a register file to buffer data for each floating-point unit (AReg and MReg). All these components are connected through a crossbar switch. Addresses for memory access can be computed locally by the address generation unit (AGU), or taken from the address queue (AdrQ).

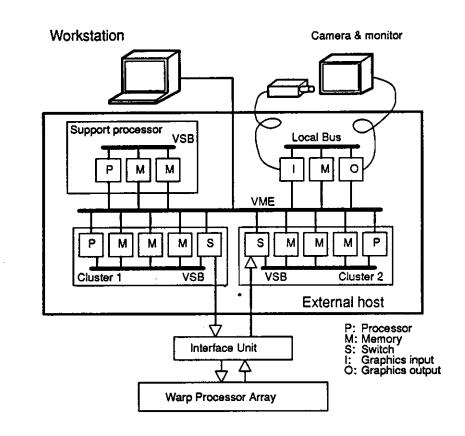

The Warp host system, detailed in Figure 3-3, comprises a standard Sun-3 *workstation* that serves as master system controller and a VME-based *external host* multiprocessor, so named because it lies outside the workstation. The workstation provides a UNIX environment for application programs. The external host controls peripherals and provides a large memory for data the Warp array will process. It also transfers data to and from the Warp array and can perform certain data operations — corner-turning or scaling, for example— without the higher overhead that a complete operating system would entail.

Both the Warp cell and IU use off-the-shelf, TTL-compatible parts, and are each im-

Figure 3-2: Warp cell data path

plemented on a  $15"\times17"$  board. The entire Warp machine, with the exception of the Sun-3, is housed in a single 19" rack, which also contains power supplies and cooling fans. The machine typically consumes about 1800W.

### 3.0.2 Chronology

We completed a two-cell Warp system at CMU in June, 1985, and then contracted two industrial partners to construct identical, 10-cell, wire-wrapped prototypes. GE delivered the first machine in February, 1986, and the Honeywell prototype arrived in June of that year. We next revised the design and reimplemented it with printed circuit (PC) technology to allow faster and more efficient production. Our revision also incorporated several architectural improvements. GE developed the PC version as a commercial product and delivered the first PC Warp machine to CMU in April, 1987. Design work for a single-chip Warp cell implementation began in 1986 with the collaboration of Intel Corporation.

Figure 3-3: The Warp machine host system

#### 3.0.3 Evaluation

We have evaluated Warp's architecture and compiler extensively, measuring several overall system performance factors and comparing them to other machines [Lam 87, Annaratone et al. 87a]. For applications in robot navigation, signal processing, scientific computation, and computer vision research, Warp is typically several hundred times faster than a VAX-11/780 class computer.

In the typical case with unidirectional data flow, the array's composite computational rate is roughly the cell count times each cell's throughput. For balanced computations, where the compiler can fully occupy both adders and multipliers, we can thus expect 100 MFLOPS total. However, because each Warp cell has multiple parallel functional units, an underutilized resource will degrade bandwidth, and so a cell's actual performance will depend upon the program's operation mix. For instance, in a computation containing only additions and no multiplications, the maximum achievable performance falls to 50 MFLOPS. Our studies of scheduling efficiency have shown that the compiler exploits the parallel and pipelined functional units quite effectively. In a sample of 72

programs, Warp achieved a mean computational speed of 28 MFLOPS with an 18 MFLOPS standard deviation.

# 3.1 Developing the Architecture

The Warp machine represents Carnegie Mellon's second-generation effort in systolic systems. We designed its predecessor, the programmable systolic chip (PSC), as a single-chip microprocessor building block for constructing large systolic arrays. While the PSC successfully demonstrated the idea's feasibility, we soon recognized its limitations: It was difficult to program, slow compared to special-purpose arrays, and capable of only integer arithmetic. Fortunately, a major advance in commercial chip technology occurred just as we commenced work on Warp. Weitek's floating-point chips, first of their kind, significantly eased the task of building systolic systems with truly powerful cells.

Running as an attached processor, Warp forms the high-performance heart of an integrated, general-purpose system. Warp offers parallelism both across the processor array and within individual cells. Each array is a VLIW (very long instruction word) machine with multiple pipelined functional units, all independently controllable. Users can access array-level parallelism directly, and through the W2 compiler, can exploit cell-level parallelism. This flexibile control represents a key to Warp's power.

### 3.1.1 Powerful systolic cells

Previous systolic systems have typically employed numerous small cells. For Warp, we chose to pursue a design that uses a few, powerful cells in a simple linear array. Our work demonstrates the concept's feasibility: Warp efficiently supports several types of parallel computation.

### Coarse- and fine-grain parallelism

Warp's powerful cells support coarse-grain parallelism efficiently. With its own program memory, program sequencer, and data memory, each cell can operate independently. The data memories (4K words in the prototype and 32K words in the PC version) are relatively large for systolic array designs. Big data memories allow individual cells to sustain high computing rates without imposing increased demand on available I/O bandwidth [Kung 86].

Fast communication between cells also makes Warp efficient for the fine-grain parallelism typically found in systolic processing. At 20 Mword/s, Warp's inter-cell I/O bandwidth exceeds that of other processors offering similar computational power and allows neighboring cells to exchange large volumes of intermediate data.

### Local and global operations

Systolic arrays are known to be effective for *local* operations, where each output depends only on a small corresponding area of the input. Warp's large memory and high I/O bandwidth also enable it to perform *global* operations, where each output may

depend on a large portion of the input [Kung and Webb 85a]. Computations involving such global operations include FFTs, component labeling, Hough transforms, image warping, and computations such as matrix multiplication or singular value decomposition. Warp's ability to perform global operations significantly extends its computational domain.

### 3.1.2 Systolic communication support

In systolic computing, unlike other forms of interprocessor cooperation, data passes directly from one cell's data path to its neighbor's, without going through memory. Such communication, transferring individual words, is inherently fine-grained and must be fast and inexpensive. When we began the Warp project, architectural support for this kind of communication was not well understood. Our goal was to provide an efficient communication mechanism suitable for a programmable, general-purpose machine.

One of our initial objectives was a machine that could implement existing systolic algorithms. We began by studying previous designs and identifying the dataflow mechanisms they employ. Many such algorithms use programmable delays to synchronize data streams, and we considered adopting this strategy. A highperformance, programmable processor, however, requires more flexible buffering and, even before building our two-cell prototype, we shifted to a queue-based mechanism.

We implemented the prototype's queues with compile-time flow control. For a substantial set of problems in our application domain, this strategy serves adequately. Applications that permit compile-time flow control include both homogeneous and heterogeneous programs, but not those incorporating WHILE or FOR loops with dynamic bounds. Runtime flow control, while more versatile, can be difficult to design, implement, and debug, so we postponed that refinement. Our redesign for the PC Warp provides run-time flow control and supports the full range of dynamic control flow requirements.

In our first, two-cell machine, receiving cells controlled data latching into the queues. The strategy required close cooperation between sender and receiver and the tight coupling resulted in tremendously increased code size. We improved the situation in the ten-cell prototype. There the sender signals the receiver's queue to latch the incoming datum.

We implemented the prototypes' queues with RAM chips, intending to support both FIFO and random access disciplines. However, there was only a single pair of hardware pointers associated with each queue, and the pointers could not be read under program control. Because the pointers had to be changed when the queue was accessed randomly, it was impossible to use the buffer both for communication and as a local storage element. To improve the array's efficiency, we employed FIFO chips for the PC Warp's queues. The change permits larger queues and relaxes execution coupling between communicating cells by allowing them to send and receive data in larger bursts and at different times.

### 3.1.3 Inter-cell control coupling

#### Localized control

Warp's long (272-bit) instructions make it awkward to broadcast instructions to all cells or to propagate them between cells. Moreover, even if cells execute the same program, their computations must often be skewed to delay each cell with respect to its predecessor. To resolve these problems, we chose a MIMD strategy, where each processor has its own control path. Independent control supports both homogeneous computing, the prototypes' computational model, and heterogeneous computing [Annaratone et al. 87a].

The local sequencer also supports conditional branching efficiently. SIMD machines achieve branching by masking, and execution time is the sum of times for branch's THEN and ELSE clauses. With Warp's local program control, an individual cell's data can determine which branch to follow and a conditional statement's execution time reduces to that for the clause selected.

### Address generation

For the prototypes, we lacked the VLSI address-generating units (AGUs) that later became available. Thus we chose to generate all common code, including addresses, on the IU and to produce data-dependent code on-cell using the floating-point arithmetic units. This strategy allowed us to handle homogeneous programs—with some restrictions—by paying an execution-time price.

Each PC Warp cell, however, contains an AGU that enables it to support more diverse applications [Annaratone et al. 87b]. With its own AGU, each cell gains both independence and efficiency. Hardware flow control of queues and independent functional units allows individual cells to execute different programs with arbitrary, data-dependent control flow.

# 3.1.4 Gaining programmability without sacrificing efficiency

One goal in designing the Warp processor was to make the achievable bandwidth as near the Weitek 10 MFLOPS peak as possible. Our strategy was to support direct user/compiler access to datapath parallelism and to make this parallelism easy to exploit [Annaratone et al. 87a]. Warp's wide instruction format provides the key link between the architectural level and datapath parallelism. A dedicated instruction field controls each datapath component and all functional units can be programmed to execute in parallel. Such orthogonal structure in the microinstruction word facilitates scheduling, since schedules for different components do not interfere.

In designing the data path, we ensured that scheduling a resource depends only on the functional unit's availability, and not on other resource schedules. Our approach was threefold. We first provided sufficient internal data bandwidth by connecting all functional units through a crossbar. This approach simplifies scheduling since, unlike a bus-based system, the process need not await an available shared channel. Secondly, we incorporated internal storage to support the two floating-point processors. These high-speed units can consume up to four data items and generate two results per cycle. Our design uses a five-port, 32-word register file to buffer operands and intermediate results for each processor. Finally, we provided three main datapath sources and drains —two queues and a local memory— and a large backup memory for the register files. When functional units can operate directly on data arriving at the queues, the main drains/sources together offer a data flow rate that matches datapath processing. The register backup increases memory bandwidth and improves throughput for those programs operating mainly on local data.

### 3.1.5 An integrated, general-purpose host

The Warp array can consume up to five million words each second and generate an equivalent output volume. Designing a host system whose capabilities match Warp's I/O bandwidth posed a significant challenge. We also wanted an open system that we could easily extend as better technology became commercially available.

Two design features contribute to high-speed performance in our host/Warp interface:

- Two clusters within the external host system, as Figure 3-3 illustrates, handle Warp's input and output [Annaratone et al. 87a]. One supplies data to Warp and the other receives results. Each cluster consists of a Motorola 68020 microprocessor and a large local memory. In the PC Warp machine, each cluster also has direct memory access (DMA) capability. For sequential data transfer, DMA permits a transfer in less than 500 ns/word. With block transfer mode, transfer time reduces to about 350 ns/word. Non-sequential transfer speed depends on the complexity of the address computation. For simple address patterns, one 32-bit word is transferred in about 900 ns.

- Data packing and unpacking reduce the host/IU bandwidth requirement by a factor of two to four. In signal, image, and low-level vision applications, input and output data are usually 16- or 8-bit integers. These data can be packed into 32-bit words before transferral to the IU, which then unpacks the data into two or four 32-bit floating-point numbers and sends them on to the Warp array. The reverse operation takes place with the array's floating-point outputs.

We have achieved an open system design by using industry standard VME/VSB protocols. This strategy enables us to employ off-the-shelf components for all external host boards except the crossbar switch. Using standard boards allows us to take advantage of commercial processors, I/O boards, memory, and software. Moreover, standard boards provide a growth path for future system improvements with a minimal investment of time and resources. During the transition from prototype to production machine, for example, we introduced faster processor boards (16 vs. 12 MHz) and larger memories and incorporated both into the host with minimal effort.

Our standard-parts approach to building the host produced two other benefits. It al-

lowed us to concentrate on the array's architecture and sped our implementation of the prototype. Having a prototype early aided development by giving system designers realistic feedback about constraints in the hardware implementation and provided a base for software and application developers to test out their ideas.

# 3.2 Software system

Although we originally intended to provide only minimal software support for Warp, it quickly became obvious that we needed a high-level language and compiler to make the machine truly usable. In addition to increasing the Warp machine's utility, our work on Warp's W2 language and compiler provided a critical tool for evaluating alternative design strategies and significantly influenced Warp's architectural evolution. Designing and implementing a compiler requires a thorough study of the target machine's functionality. The systematic analysis we undertook in developing W2 allowed us to uncover problems that might have otherwise gone undetected.

### 3.2.1 Language design

To achieve both generality and efficiency, the user must retain control of how a computation maps across the array. At the cellular level, however, automatic tools can do better. Parallelism available within Warp cells makes hand coding impractical.

We set out to develop a general systolic language (W2) that would allow the user to specify each cell's actions individually while still permitting access to array-level parallelism. Since the user may sometimes need to restructure a sequential algorithm to exploit systolic cells, we also wanted to provide appropriate high-level constructs [Lam 87]. Previous systolic array notations were unsuitable because they typically assumed a simple, repetitive problem domain and dedicated, custom hardware. Our design goals for W2 were:

- Generality sufficient to enable a user to express all programs that the flexible, programmable hardware can support, such as those employing general and data-dependent control flow

- A language design allowing us to build a complier that can generate efficient execution code.

For communication between cells, W2 employs an asynchronous communication model. We chose this strategy because it offers programmability and allows compiler optimization. With appropriate techniques, we can compile unidirectional systolic array programs that use asynchronous communication into highly efficient code. The high-level semantics of asynchronous communication permit "code motion" whereby the compiler can redistribute instructions among basic code blocks and more effectively util-ize Warp's intra-cell parallelism [Lam 88a]. W2's asynchronous communication model is even applicable in simple implementations, such as the Warp prototype machines, that have no dynamic flow control hardware. This flexibility derives from W2's efficient compile-time control flow algorithm [Gross and Lam 86].

SYSTOLIC ARRAY MACHINE

### 3.2.2 An optimizing compiler

#### Code optimization

To exploit the parallelism a VLIW machine offers, "global scheduling" techniques are essential. These techniques, which overlap operations from different basic code blocks, are vital for heavily pipelined and horizontal processors because the basic block structure alone offers very little parallelism. Global scheduling, in turn, relies on accurate global data dependency information. In developing Warp's programming language, we have addressed both data dependency issues and methods for scheduling VLIW machines.

We have implemented a sophisticated global flow analyzer that generates flow information accurate up to the level of individual array elements. It analyzes data dependencies between array accesses throughout a program, within basic blocks and different iterations of a single loop, and across different loops. Labeled arcs in the flow graph capture the derived information, which is then readily available for various code optimizations.

For global scheduling, we concentrated on two techniques: *software pipelining* and *hierarchical reduction* [Lam 88b, Lam 87]. Software pipelining exploits the repetitive nature of innermost loops to generate highly efficient code for processors with parallel, pipelined functional units. We showed that software pipelining is a practical, efficient, and general technique for scheduling the parallelism in a VLIW machine. We have extended previous software pipelining work in two ways. First, we demonstrated that, using scheduling heuristics, we can obtain near-optimal results for all loops. We have improved and extended previous heuristics and introduced a new optimization technique, "modulo variable expansion." Our approach has part of the functionality of the specialized hardware proposed for the polycyclic machine, and thus allows us to achieve similar performance.

Our hierarchical reduction scheme allows us to reduce an entire control construct to an object resembling an operation within a basic block. Previously, software pipelining has been applied only to loops whose bodies are straight-line code segments. Heirarchical reduction allows us to apply software pipelining to arbitrarily complex loops. The significance is threefold: All innermost loops, including those containing conditional statements, can be pipelined. Secondly, if the number of iterations in the innermost loop is small, we can pipeline the second level loop as well. Lastly, hierarchical reduction diminishes the start-up cost penalty for short vectors.

#### Multiple code generators

Since Warp cell computations are tightly coupled, the compiler must extract data address computation and host communication from the user's program and implement them on the IU and the host. Our design achieves this parallelism by decomposing a program's flow graph into three subgraphs for the cell, IU, and cluster code generators. From the cell code, the compiler extracts timing and sequencing information for the input to and output from the array (including addresses on the address queue). The IU and the host code generators then use this information [Gross and Lam 86].

### Retargetability

We have structured the W2 compiler so that we can easily retarget it to handle architectural revisions [Gross and Lam 86]. The compiler was first built for the wirewrapped Warp prototypes, but has since been retargeted for both the PC Warp and iWarp. Many compiler parts can be reused without modification on different architectures. The flow graph representation, for example, is machine-independent, as are the modules that operate on the flow graph: the parser and the local and global dataflow analyzers. The Warp machine's simple, orthogonal instruction set also makes backend modules reusable: scheduler, register allocator, and code emission units in the cell code generator.

### 3.2.3 Programming environment

The primary objective of the Warp Programming Environment (WPE) is to simplify the use of the Warp machine. Our design provides a uniform environment to edit, compile, debug, and execute W2 programs, supports efficient multiple user access, allows users to access multiple Warp machines, and provides network transparency [Bruegge et al. 87].

The WPE achieves efficiency and convenience by supporting two modes of accessing Warp. Users may opt for convenience by using the Warp shell, a command interpreter that interfaces the user to the components to the WPE. Or he may choose efficiency by programming the machine in "standalone" mode, calling run-time system procedures directly.