# NOTICE WARNING CONCERNING COPYRIGHT RESTRICTIONS:

The copyright law of the United States (title 17, U.S. Code) governs the making of photocopies or other reproductions of copyrighted material. Any copying of this document without permission of its author may be prohibited by law.

# TASK SCHEDULING ON MULTIPROCESSORS

.

٠

by

R. Mehrotra & S.M. Talukdar

December, 1932

DRC-18-55-82

# TASK SCHEDULING ON MULTIPROCESSORS

Ravi Mehrotra

Sarosh N. Taiukdar

Department of Electrical Engineering Carnegie-Mellon University Pittsburgh, Pennsylvania 15213

## ABSTRACT

The paper describes a technique for estimating the minimum execution time of an algorithm or a mix of algorithms on a multiprocessor. Bottlenecks that would have to be removed to further reduce the execution time are identified.

The main applications are for designing special purpose. dedicated multiprocessors. Today, a bewildering array of computer components \* processors and devices with which to interconnect them - are available. The future will bring even more of these components. To intelligently choose mixes of them one needs systematic procedures.

In the procedure of this paper the multiprocessors are modelled by P. a set of processors and R, a set of resources that the processors can use. The algorithms are modelled by T. an ordered set of tasks. The problem of optimally assigning the processors to the tasks while meeting the resource constraints is NP-complete. A heuristic using maximum weighted matchings on graphs has been devised that is extremely fast and produces solutions that are reasonably close to the optimal solutions. The heuristic has been coded in Fortran and illustrations of its use included.

## 1. INTRODUCTION

## 1.1 The General Form of a Distributed Multiprocessor

Most existing codes have been written for Von-Neumann, general purpose computers with targe virtual memories. However, it is now possible to assemble non-Von-Neumann architectures, often using just off-the-shelf components. The general form of one such class of architectures is shown in Fig. 1.1. The processors may have diverse processing, input and output characteristics and may be physically close or geographically separated. The communication network may use a transmission means (such as wires.satellites and optical fibers) and a variety of configurations (such as stars.trees and loops). We will elaborate on these alternatives in 1.4 and 1.5.

## 1.2 A Very Brief Review of Previous Work [1]-[5]

Research into the use of special computers for power system appreciations has concentrated on three limited possibilities:

- 1. The exclusive use of large vector machines like the CRAY-1

- 2. The combination of a host machine with an array processor like the AP120-B.

- 3. Homogeneous multiprocessors (large numbers of identical processors symmetrically interconnected)

These research efforts have met with some, but not spectacular, success. The reason is that power system algorithms contain a wide variety of tasks. Some work well on vector machines and array processors, others do not. Some work well on homogeneous multiprocessors. others do not. Therefore, the exclusive use any one limited hardware arrangement will inevitably lead to severe bottlenecks.

## 1.3 The Design Problem

To alleviate bottlenecks we need to ask the question: How can we assemble a computer system with the diverse skills needed to efficiently process all the tasks in a given power system algorithm or mix of algorithms? One ••••a\* to go about answering this question is to take the folio.-.'no four steps:

- 1. Identify the computer components that are no\*/ available or will soon be available.

- 2. Categorize the tasks or, alternately, identify a set of primitives from which the tasks can be synthesized.

- 3. Determine how effective each component is for each primitive.

- Devise a scheme for assembling mixes of components to best handle given mixes of primitives.

The result of taking these steps will be a computer of the type shown in Fig. 1.1 and dedicated to a mix of algorithms.

The emphasis of this paper is on step 4. We will discuss the other steps but to considerably lesser degrees.

## 1.4 <u>Network</u> <u>Alternatives</u>

Computer communication networks can be divided into three categories.

## UNIVERSITY LIBRARIES CARNEQIE-MELLON UNIVERSITY PITTSBURGH, PENNSYLVANIA 15213

1

M « MEMORY P « PROCESSOR

Fig. 1.1 A General Fdrm of a Multiprocessor.

1. Large scale computer networks such as ARPANET which is designed to interconnect dispersed and dissimilar computers, allowing users and programs at one computer center to access and interactively use facilities at other, geographically remote, centers. Other examples are TYMNET and GE networks which facilitate commercial time sharing [63.

Loca! Area Networks [7]-[11]. 2. When the processors connected to the communication network are within 2-3 kilometers of one another, the network is called local area network. Local area networks for minicomputers such as Xerox . Corporation's ETHERNET and Zilog Corporation's ZNET have now been in existence for sometime. The formats, protocols, operational sequences and logical structures for functions needed to achieve meaningful communication among processor units connected to such networks are readily available. Infact the processor interfaces will soon be available on VLSI chips and their costs are expected to drop to the range of hundreds of dollars.

2. Bus Structures. Processors can be interconnected ". :...-f. \* 'T-'JCT  $c^{-1}$  s?". ICtures is posriMe [12]-[16]. An example of a s^ple bus structure is the UNIBUS of a PDP-11 which can be used to connect a host computer to a number of peripheral processors. Examples of more complicated bus structures are those used in multiprocessors such as C.mmp, Cm\* and BBN PLURIBUS.

## 1.5 Processor Alternatives

- T. -

services and the second second

The number of processor alternatives is extensive and growing. The alternatives can be categorized on the basis of a number of factors such as speed, availability and cost. Whatever classification scheme is used, it is difficult to keep the categories from overlapping. One set of categories is:

- Special purpose, dedicated VLSI processors [171-[24] that will soon be appearing in large numbers to do tasks like matrix multiplication and LU factorizations very fast.

- Relatively inexpensive programmable processors including array processors (such as the AP 12OB. FPS 100 and FPS 164) and microprocessors (such as the Z80 and Intel's 8086).

- · · ·

- Bit slice processor elements (such as Texas Instruments S481/LS480 that can be assembled into systems for specific applications.

- Minicomputers like DEC'S VAX/780 and PDP-11/70.

- Large, general purpose machines like IBM's 3030, Burroughs B5000, CDC's 7600. as well as large vector machines like the CRAY-1 and STAR-100.

#### 1.6 Goals and Organization

In the past, computer alternatives were evaluated by tedious benchmarking or almost as tedious simulations, in view of the variety of alternatives now available, neither of these approaches is practical until the very last stages of the search for a computer system. For the early parts of the search one needs evaluation tools that are  $qixc^A$  and easy to use. The rest of this paper will be devoted to the development of one such toot and to a simple example of its use. Specifically, the tool is an efficient, interactive program that estimates the minimum execution time and identifies the bottlenecks for a given mix of tasks on a given mix of computer components. The results enable the user to determine whether the mix of components is promising and how to incrementally change it to improve performance.

Section 2 gives a formal aescnpnon of the p'OLte-r. we shall consider. Section 3 indicates a solution metnoa after a brief review of methods that have been used to solve similar problems. The procedure described in section 3 has been coded as a user friendly interactive program in FORTRAN on DEC-20 system and is used to study a proposed multiprocessor architecture in section 4. Section 5 summarizes the results obtained so far and lists further work to be done.

## 2. MATHEMATICAL FORMULATION OF THE PROBLEM

This section establishes the basic vocabulary for the remainder of the paper and gives a precise mathematical formulation of the problem to be considered.

#### 2.1 Algorithms

An algorithm A is described by  $A^{*}{T.*}$  where T and c are sets defined as follows:

T is a set of tasks {T<sub>r</sub>, T<sub>A</sub>, ..., T<sub>N</sub>} and the set **a** denotes the partial ordering relation on T such that T<sub>p</sub> **a** T implies that the execution of tasks Mcalled the successor of **Tb**) cannot begin until the execution of T**p**(called the predecessor of T<sub>s</sub>) has been completed. We will represent an algorithm A tDy a directed graph called the task graph G<sub>A</sub>(V.E) of A so that there is one node in V for each task in T and and one arc in E for each relation in partial order c. When a is empty the tasks are called independent. It is assumed that the tasks to describe A are chosen from a finite set of tasks T<sup>p</sup> « {T<sup>A</sup>. T<sub>2</sub><sup>P</sup>... T<sub>n</sub><sup>P</sup>) of n primitive tasks. Each task T<sup>\*</sup> < T corresponds to some primitive task T<sub>y</sub><sup>p</sup> \* T<sup>p</sup>.

# 2.2 <u>Multiprocessors</u>

We may think of the multiprocessor architecture at a high level as having been assembled from processors that execute tasks in  $T^p$  with the use of certain resources such as disk drives, tapes, memory and the interconnecting devices including the buses and data links that form trife communication network of the system. The multiprocessor system MP with M processors and L resources will be denoted by MP{P,R> where  $P \ll \{P_1, P_r \ldots P_M\}$  is a set of M processors and R MR,  $R_2 \ldots R_L$ ) is a set of L resources.

· · . .

## 2.3 Algorithm - Multiprocessor Interaction

Each task T < T may be executed on any processor in P.We define a function  $(TWt, ..., t^{A}, ..., t_{M>})$  so that the value rf t represents the exnecterl time it tales to evrcute task T on processor P. Furthermore we define a function  $r(T)^{*}(r_{1}^{*}, r_{2}^{*}, ..., r_{d})$  to represent the resource requirements of task T such that r, is equal to the amount of discrete resource R needed while executing T, and y?(RJ is the total units of  $R_{x}^{*}$  in the system.

## 2.4 Execution time of A on MP(P.R).

Let r(I) represent the starting time of the execution of task T<sub>(</sub> • T.'

Define  $X(k) \ll 1_{(i)}$  if task T is executed on processor P<sub>(</sub> at time k and zero otherwise! It is assumed that time is measured in terms of equal and indivisible units. Using the notation 'introduced in this section we define a feasible schedule to be a mapping ¥: T->I such that the following 3 conditions are satisfied. (1 is a one dimensional space of integers representing time).

C1:

$$\sum_{i=1,...,k=1}^{N} \sum_{j=1,...,k=1}^{N} k^{i} = 1$$

for j\*l...H, all ket

C2: If **T**, **T**, then

$r(\tau_j) \geq r(\tau_j) + \sum_{r=1,\dots,r} r_r X_{r+1} U$  for i,j=1..K, all kel. C2:  $\mathcal{A}(\mathbf{R}) \geq \sum \sum_{r=1,\dots,r} r_r X_{r+1} U$  for all kel.

$$(r_1) = r_1, r_2, r_3, r_{iy} = \Lambda_{pj} \cup r_{f}$$

CI is needed to avoid the assignment cf a task to more than one processor. C2 is a statement of the procedure constraints of A. C3 is needed to ensure that the resources required by a job will be available while the job executes.

Corresponding to each feasible schedule M: T->I we define the execution time of the algorithm A on MP as :

# L<sub>A</sub><sup>MP</sup> « jŋjŋ {3r(k)«0 for i«Lm, j«UN}

Thus the problem of finding the optimal assignment of tasks in the algorithm A on a multiprocessor MP so as to minimize the overall execution time may be stated as GSP  $\pounds^{G}$ SP] minimize  $L_A$

subject to ¥:T->I

We can find a lower bound  $L_A^{\circ\circ}$  on  $L_A^{MP}$  as follows:

For every node  $n_i t G(V.E)$  define the weight of  $n_i$ ,  $W(n_i)$  as

W<ŋ>min (t,,. t<sub>2i</sub>. . . . tJ

Define the length of a directed path from node n to node  $n_t$  to be equal to the sum of weights of all the nodes in the directed path from  $n_s$  to  $n_t$ . The longest directed path from a node with no predecessor to a node with no successor represents a lower bound on *ij\**. This lower bound  $L_A^{\circ\circ}$  is obtained by assuming that all the tasks in G<V,E) are assigned to the processor on which they take minimum execution time and there is a sufficient number of processors and resources in the system.

If the solution to GSP gives a value of  $L_{,}^{,\mu\nu} > L_{,}^{,00}$  then the elements of the set P and R may be modified<sup>A</sup>to reduce the difference between  $L_{,}^{,**}$  and  $L_{,}^{,\circ}$ . This allows us to reconfigure a multiprocessor system that is most suited for executing the specific algorithm. The solution procedure (see section 3) used to solve (2.4) enables us to identify, what limits performance, thus suggesting a natural modification of the set P and/or R.

## 2.5 A Cost Constraint

Let CP(P) represent the cost of processor P<sub>(</sub>. i«1...M.

A cost constraint may be added to obtain GSPC as follows:

All processors in the set P are not necessarily used. The solution procedure would select the particular mix of processors that minimizes the overall execution time with the total cost of processors in the mix being no more than C.

## 3. SOLUTION PROCEDURE

GSP is a notoriously hard combinatorial analysis problem known as the General Scheduling Problem. This problem is MP-corr.plete. Instead of seeking polyr.crr.io! time optimal algorithms for NP-compiete problems, cne uses heuristic Vot opproAinuie? algorithms wine;, t.opfc^u..., .ci^. "good" solutions in polynomial time. Most work done m the area of scheduling has been devoted to the case when all processors in the system are identical[25]-[25]. Some enumerative and iterative techniques such as 'local search' and 'branch and bound' have been applied to subproblems of GSP [36]-[39]. But there are no heuristics for solving GSP itself and branch and bound techniques are computationally impractical for solving it.

We will proceed to develop a heuristic technique for solving GSP. The technique is based on finding maximum weighted matchings on graphs. It yields reasonably good solutions to GSP and GSPC.

The essential steps are:

- 1. Input Edge List Matrix of G<sub>A</sub>(V.E). Execution Time Matrix [t<sub>1</sub>] and Resource Requirement Matrix [r] (see Example 3.1).

- 2. Assign levels to the nodes.  $T_x$ , of the task graph GJV.E). Intuitively, levels assigned to nodes are distances from a node with no successor and represent the precedence structure of G<sub>A</sub><V.E).

- Making use of the levels of the nodes, assign corresponding tasks on the processors, disregarding the resource constraints. This step is carried out by finding maximum weighted matchings\*

- 4. Schedule the tasks on the processors they have been assigned to. taking resource constraints into account. Make a list of resource shortages if any.

- 5. Repeat steps 3 and 4 until all tasks have been scheduled.

- 6. Output the schedule and the list of resource shortages (see Example XI).

The details of steps 2-5 are given in the appendix.

The heuristic to solve GSPC is similar to the above heuristic. The cost constraint is factored into the solution process by including it in the objective function of the maximum matching problem [40]-[42].

Table ai (a). Edge List Matrix.

Table ZJ2. Resource Shortage Table.

| Task | R1 | R2 |

|------|----|----|

| T4   | 3  | 2  |

Figure 3.1. A task graph, G (V,E)

Table 3.1(b). Execution Tims Matrix.

|    | T1 | Т2 | Т3 | Т4 | Т5 | Т6 | T7 | тв | Т9 |  |

|----|----|----|----|----|----|----|----|----|----|--|

| ΡI | 2  | 2  | 1  | 1  | 1  | 1  | 3  | 1  | 1  |  |

| P2 | 3  | 1  | 1  | 3  | 1  | 2  | 1  | 2  | 1  |  |

| P3 | 1  | 1  | 2  | 4  | 3  | 1  | 4  | 1  | 3  |  |

Table &1(C). Resource Raquiniment Metarix.

| R  | Α | Т 1 | т | 2 | т | 3 | т | 4 | т | 5 | т | 6 | т | 7 | т | 8 | т | 9 |

|----|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| R1 | 3 | 1   | 1 |   | 1 | ; | 3 |   | 1 | ( | 0 |   | 2 |   |   | 0 |   | 3 |

| R2 | 2 | 0   |   | 1 | 1 | 1 | 2 |   | 2 | 2 |   | 0 |   |   | 1 | 0 |   | 0 |

#### A \* Amount of Resource.

| P2         T2         T5         T7           P3         T1         T6         TB |

|-----------------------------------------------------------------------------------|

| <b>P2</b> T2 T5 T7                                                                |

|                                                                                   |

| <b>PI</b> T3 T4 T9                                                                |

- TwneUnit 12 3 4 5

Fig&2. Pictorial Representation of the Schedule.

Example 3.1. Consider a multiprocessor system MPt'P.R) with  $P^*\{P, P_2, p_3\}$  end  $R^*(R_2, R_2)$ .

The inputs required, for task graph of Fig 3.1 are given in Table 3.1(aHc).

Table 3.1(a) is a matrix representation of  $G_A$ <V.E). The

values of [t\_] and [r\_] are specified in Table 3.Kb) and 3.1(c) respectively. (R\_,)^ units and(R\_2>«2 units. L^-3.

Fig 3.2 is a pictorial representation of the output of the procedure. Note that  $L_A^{MP*5}$ . Table 3.2 is the output which indicates the bottlenecks which must be removed to reduce the overall execution time. Task T4 could not be started in parallel with T5 and T6 because of resource shortage. It needed 3 units of R<sub>1</sub> and 2 units of R<sub>2</sub> and none were available. If we let  $\beta(\mathbf{R}_1)=6$  and  $/ft'\mathbf{R}_2$ \*4 then L would be equal to  $L_A^{\circ\circ}$ .

#### 4. BJJJSTRATION OF THE DESIGN PROCESS

The solution procedure outlined *in* the previous section has been translated into a user friendly, interactive, FORTRAN program called SNONUET. It allows the user to modify the input parameters until either satisfactory execution time is obtained, or no further improvement is possible. SNONUET has been tested on a number of randomly generated examples and it produced near optimal schedules in most cases. The purpose of this section is to illustrate some of the uses of SNONUET. To do this we will use a simple example, chosen for explanatory purpose rather than realism.

الأرابية العجر العبر جارات المراجع المراجع المتهيد

# using high level primitives.

4.1 Algorithmic Primitives

The first step in preparing the input data for SNONUET is to identify a set of primitive tasks,  $T^{p}$ , in terms of which to describe the algorithm<sup>^</sup>) in question.

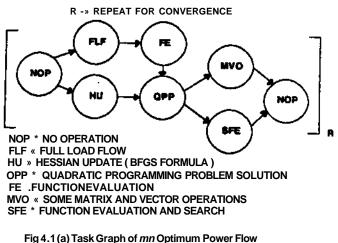

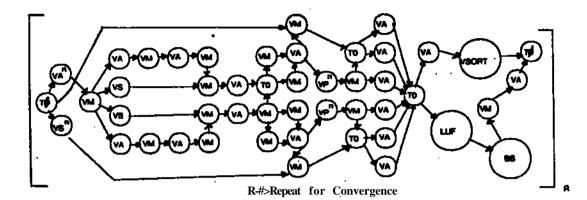

The primitives can be at various levels. Very high level primitives result in simple task graphs with a few nodes. For instance, an optimum power flow [43] can be described in terms of high level primitives by the task graph in Fig 4.1(a). Or. using the primitives given in Tatle A.",, v.c could expand each node of the task graph. The task graph corresponding to FLF is shown in Fig 4.Kb).\*

A reasonable way to proceed is to use high level primitives for the initial design and then refine the design with lower level primitives.

## 4.2 Processor arid Communication Network Alternatives

The ?frnr.1 *r.ter.* in p»ep?"»nc the input data for SNONUET is to choose the processor and communication network alternatives to be considered.

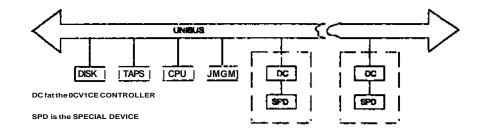

We start with a unibus multiprocessor system shown in Fig 4>2.,\*\*which is a special case of the general

## TABLE 4.1

## Set of Primitive Tasks Mnemonic

- -

. . . . . . . . .

| T  | No operation (used for synch-<br>ronlzatlon)                 | то     |

|----|--------------------------------------------------------------|--------|

| Tl | Vector Add (C* • a <sub>±</sub> + b <sub>if</sub> i«ln)<br>n | VA     |

| T2 | Vector Inner Product (C - $I tt^{h} b_{t}$ )<br><b>i=1</b>   | VP     |

| T3 | Vector Scale (b. «Ca.t 1-1a) .                               | VS     |

| T4 | Vector Divide (ba^C, 1*1n)                                   | VD     |

| T5 | Vector Multiply ( $C_{t}$ - $a_{t}b_{it}$ 1-1a)              | VM     |

| T6 | Vector Sort (arrange elements in an increasing order)        | V Sort |

| T7 | LU Pactorzation                                              | LOT    |

| T8 | Back Substitution (used to solve a set of linear equations). | BS     |

\* Page 5 \*\* Page 6

Fig 4.1.(b). The task graph corresponding to node FLF (Full loud flow) of Fig. \*1.1(a). (T)<sup>n</sup> denotes that n of (T) may be done in parallel.

multiprocessor system of Fig 1.1 - the communication network is now the data channel of the host computer. The motivation for using the common data bus is the simplicity of the interconnection, also if the communication over the bus does not limit performance there would be no need to consider more sophisticated interconnection schemes. Each special purpose device is a processor/multiprocessor realized in VLSI, with its own private memory. The unibus of the system is considered to be a resource of the system. If the total time needed for all data transfers over the bus of all tasks in G\_<V.E) at any level is found to be more than 10H of L <sup>oo</sup> then the bus is considered to be a bottleneck. The details of the bus modelling procedure are described in [42]. SNONUET finds the latest finishing time of all tasks and identifies bottlenecks. If the unibus of the system is not a bottleneck, the number of special processors of a given type may be increased to check if further reduction in the overall execution time is possible. On the other hand if the unibus turns out to be a bottleneck, we introduce another bus amongst the processors sharing the congested bus. to relieve the congestion and improve speedup. The above steps are repeated until no further reduction in execution time results.

## 4.3 Cost and Time Data

The third and the major step in preparing the input data for SNONUET is to estimate the cost of the processors and the task running times.

We consider the execution of the GJtV.E) of FLF shown in Fig 4.Kb) on the multiprocessor of Fig 4.2. Three different types of processors are considered, an array processor AP (such as AP 1208) and two special purpose VLSI peripheral processors SPI and SP2. The estimates of the execution time of the host and the three types of processors considered are listed in Table 4.3.1. The per unit cost of the three types of processors is shown in Table 4.3.2.

## 4.4 Results

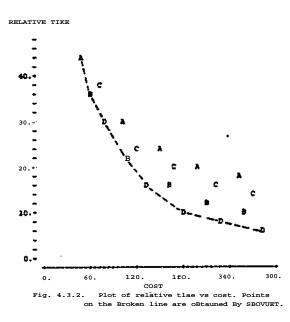

The output of SNONUET when no cost constraint was placed indicated that overall execution time could be reduced by increasing the number of APs to 5. The overall execution time obtained by SNONUET has been plotted vs the number of APs in Fie 4.3.1, after sca«inq it so that the stand alone host could sequentially execute FLF in 100 units of time.

The overall running time vs cost is plotted in Fig 4.3.2. It is important to note that SNONUET with a cost constraint

TABLE 4.3.1. Istlatt\* of Execution Tlae

| -                                                        |                                                   |                                                     |                                   |                                       |

|----------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------------|---------------------------------------|

| Prlaltlv* Task                                           | BOST                                              | AP                                                  | SPl                               | SP2                                   |

| T#<br>TA<br>*P<br>VS<br>TO<br>*H<br>• sort<br>UJF1<br>*J | 0<br>100<br>1100<br>1000<br>1000<br>4\$50<br>4000 | 0<br>35<br>410<br>340<br>340<br>340<br>5000<br>3000 | 0<br>22.<br>00<br>00<br>00<br>700 | 0<br>ei<br>70<br>00<br>00<br>m<br>400 |

| Processor   | Cost |

|-------------|------|

| AP          | 50   |

| SPl         | 10   |

| <b>SP</b> 2 | 20   |

| HOFT        | 0    |

|             |      |

generates only the points on the broken line. The other points correspond to mixes of processors that should not considered because they provide lesser speedups for the same cost.

Rg4.2. A Unfeus multiprocessor system.

## 5. CONCLUSIONS

This paper has described a systematic procedure that is useful in the selection and design of dedicated multiprocessors. The procedure has been coded into an interactive FORTRAN program called SNONUET.

Before SNONUET can be used one must break the algorithm^) into ordered tasks, select a set of processors for consideration and select a set of resources for the processors to use. One must also estimate the time and resource requirements for each primitive task. SNONUET will then schedule the tasks on the processors and identify bottlenecks that are must be removed if further decreases in the overall execution time are to be obtained. One may include the cost of the processors and an upper limit on what the system is to cost. SNONUET will select a subset of processors and schedule them so as to minimize the execution time of the algorithm(s) and satisfy the cost constraint. This procedure enables us to plot the optimal speedup vs cost for a fixed communication network. It would be very useful when selecting a set of processors from those commercially available, when a local area network is used as the communication netork of the system.

The example in Section 4 was chosen to illustrate the use of SNONUET, and not as a realistic design exercise. It could however be used for designing multiprocessors if they were to be dedicated to solving load flow problems.

Some further work needs to be done to obtain a better way to model the communication network when its architecture is specified and queueing delays are involved as a result of packet switching. In the present model, for each task requiring the communication network, expected queuing delays are added to the message transit times. The sum is treated as a deterministic time for which the resource corresponding to the communication network may not be used by another task. This is a major drawback of the procedure and we are working towards a remedy.

## 6. ACKNOWLEDGEMENT

This work was supported in part by the Electric Po.ver Research Institute under project RP1764-3.

#### References

- Chem. F.M., "Evaluation of an Army Processor for Power System Applications.." 1979 Power Inquisiry Computer Applications Conference ProceetOMigs.. CEE. 1975. pp. 345 350.

- Podmo\*. tLjnmnon, ULwangM. Britten. .Land \finnant S.. "Appaĉafcons of an Array Fracement for Paner System Network Comparison." 1979 flMWr taOustry Compute Applications Conferences Proceedings., EEE.T979. pp. 32\*330.

- Happ, K.K. PMte. C and Wbgan, K. A., -An, . . . . nt of Cowpmor Tactmotogy tor Large Scale Power System Simulation.," 1979 Paper Industry Control of Applications Conference Proceedings, IEEE, 1979, pp. 316-329.

- an \*. F. M., van Nam J. E. Kang and Seng-Caul. -Tha uat of a Mathematimum Hetwerk for the Transient Bandidy Problem," 1979 Power Industry Computer Applications Conference., IEEE, 1979, pp. 327-344.

- PMdiard, ft and Petäa. C "High-Spaad Fewer Fieae Laws Allecting Actionate (APRAY) Proceedings." 1981 Plrawr to+tmy Cam'v'r \*\*\*cmam Canfinwice"... CEE. fcfay 54 1981. pp. 149-153.

- Schweitz, Mache, Computer Combusider Network Design and Analysis, Prehice-Hell, tec., Englewood (2016, N.J. (20182), 1077.

- Unger, Brisk, Statuteth, Dan-, Lomam, G.eg., Billion, PML, Ha\*\*\*, CaroL and Jain. Navinda... "An QASS Emutation of DIST discretance Measure"..." «£ kUC/tO. Attgust W82.a. 7045.

- a Materiality, R. M. and Baggs, D. R., "Elitaritatic Distributed Packet Statisticity for Local Computer Networks.," CDMM, ACM, Vol. 18, Ho. 7, July 1976, pp. 385-494.

- a. Thurbar. Kmmm J.. Fmoawt and Harvey A.. "JachaactMral Conaidaraaont tor Lpcat Computer Networks." «nx. Hm M7Com. Obstrauted Computing Systems, Oct 1978, pp. 131-142.

- 10. Afat Map Land Von, OBMJ.. The Chinging Economics in Computer and Terminal Interconnection on Convious, "Technical Riseau, and Long with total.

- 11. OaM. Vegan IC. IJao of aMioto Inilii/Bitii in \*e Xonx Moftaorii Syatam." Computm. OcU\*tri9K.pp.«91.

- Wolf, W. A., "Britisanguter Complexat: Propriet and Prospectr," Comprom Seiane" m<sup>+</sup> Scientific Companying, Crogat J.M., a<sup>+</sup>., Puc 01 \*• 3rd CASE Conf. on Saanaae Computing, Agei 1976, pp. 393-306.

- Stano, H. S., "Computer Architecture in the WHO's," Computer Salarse and Scientific Computing, Orlega, J. M., ed., April 1979, pp. 205-201.

- Lenahan, J. J. "Performance of Cooperative Lenary Coupled Microgroups Architectures toonmmraea^aOaiaBMM Tark,," IEEE Trans. Vol. C-ID, No. 2, Petr 1980, pp. 101-179.

- Fanaoi. Cdw^d P., Ghaw, W. and Ji+I++++", PH\*p C, "A Concurrent Contract Architecture and a Ring Boatd IIIUmimalion.," Teen, report. Cawpming Libborshify, University of Neur Costly upon Type, Expland, 197.

- Hank, J.Archer, and Smith, David R., "Elevatelian Experiments of a Trap Organized Mathematical Activity of the Annual Symposium on Computer Architecture, April 1979, pp. 28-30.

- Kump, S.Y., "Matrix Data: Plan Language for Matrix Operations on Deficated Army Processors.," Proc. ECC70 1981, The Huges, The Mathematics, Aug 1981, pp. 393–398.

- Yung, S.Y. and Pan, D.V. Shankar, "Highly Parallel Architectures for Solving Liteur Equations," Proc. ICASSP 1981, Algona, 1981, pp. 39-48.

- Kung, S. Y., Ann, K. S., Rao, D. Y. Bhashar, and Hu, Y. H., "A Matrix Data New Language / Architecture for Panelist Matrix Operations Stated on Computational Woodcurt Concept.," *Correspondence University Conference on VLBT Systems and Contrastational*, Oct 1981, pp. 208–204.

- JO. •uric Mnha Hand Maad. Carwar A.. -MSartal amar Product Proceedings of the Second Catherin Continuings of VLSL, Strendby 1981,.

- Kang, S. Y., "VLB: Area Processes for Signal Processing." Conference on Advance Represents in Internation Consults, MIT, Combinities, MA, January 35-30 (1990).

- Bastar, J.M. and Whitehean, H.J., "Architectures for Resi-Time Mattin Operators," Proceedings. (OphIC, Neurality 1980).

- Karny, H. T., "Lat's Design Algorithms for VLSI Systems." Proceedings CALTECH Conf. on VLSI January 1977, pp. 65-90.

1.1.1.

- Kang, H.T., "The Brandow of Parallel Algorithms." Advances in Computers. VW.11.1MO. pp. 65-511.

- 28. Callman, E. G., addars, Computer and Job-Shop Sphemistry Theory., Wiley, 1979.

- Lans, S., and Sachi, R., "Want Case Analysis of Two Schwinking Algorithms.," State Journal of Computing, Vol. 6, 1977, pp. 518-538.

- Gayal, D. K., Schooluling Equal Execution Theor Tests Under Unit Resource Restriction., PhD description, Washington State University, 1976, Computer Science Copyrights.

- Laung, J.Y. T., "Dounds on List Scheduling of UET Table Web Restricted Resource Constraints," Information Processing Latters, Vol. 9, 1079, pp. 107-170.

- Jolle, J., Poular Computies: Systematics. Establishing and Echemics. Pro MeanMaker, Intersections, Institute of Technology, 4978, Department of Electronic Engineering and Computer Science.

- Ulimen, J.D., "BP-Campiole Schooluling Problems," Computer and Systems, 1975, pp. 204-303.

- 31. Lines, J.D., "Palaenet Compton Schulzing Publisms." Operating Systems Reven. 1973, pp. 66-101.

- Caliman, E. J., editer, Complexity of Singuranting Problems., Wiley, Computer and July Shap Schoolding, 1978, pages 139-194

- •runo. J.-. Cofciw. E. J. an\* Safe It. "Enhancing Inducation Tasks to Platece Mean finaNag Taw.." CAOML11:24 pp. 31% > 7.

- Landra, J.R. and roweoi, M.n.i H.Q., -CowpHiiHji of Scheduling Under Procedures Contraction," Operations Research, 1970, pp. 25-26.

- S Uoytf. E.L. Se»i#M⊳m T M\*Sil I W I •#\* I i i i miii. 1940 dagaatalaan k M.I. T<sub>M</sub> May 1W0. Competence « f *Btttnat* Eia,\*M mg and Competer Science

- S. Hold. M and Karp. R., "A Cytantic Programming Approach to Bayanning Problems.," Sider JL Appl «+» ta 1.1W2.P", itS-210.

- 7 37. Marweitz, E. and StfMi. S.K..-CMd wd Aggregatings Algorithms for Scheduling Mandematical P>offMWI.,~ JMCtf2X2. tVr\*. pp.317-327.

- Callman, E. G., adlor, Enumerative and Revalue Computational Approaches, John Wiley & Serie, Ver, Computer Joh/Shop Scheduling Theory, 1975.

- Krone, M. J., Hauristic Programming Applied in Scheduling Problems, PhD description, Principus University, 1970.

- Edmands, J. "Matching: A well Salved Clean of Imager Linear Programs.,~ Froc al \*\* C\*9\*f int. Co\*. on Como.jShuctures and Ther Appl., Gordan and Brasch, 1019, pp. 10-30.

- Matricina, R., "Maximum Weighted Matchings on Elevate Graphs.", Technical Report, Carnege Mellen University, Datambar 1982.

- Makeura, R., "An Algorithm Based an Pinging Weighted Matchings in Graphs to Scholule Tasks on Multiprocesses.", Technical Report, Conteger Maler Minorphy, December 1992.

- Talvinter, S. H. and Girsa, T. G., "A Past and Rebust Variable Matrix Mathematics Power Flows," *IEEE Transactions on PAS*, Vol. PAG-101, No. 2, Pob 1002, pp. 415-425.

## **APPENDIX**

The nodes,  $T_{x>}$  of the task graph  $G_A(V,E)$  of an algorithm A **sre** assigned two levels  $L^B(T_x)$  and  $L^*(TJ)$  by the algorithm below

#### AlQorithm Asstan Levels:

1. If

$$\underline{\Gamma}$$

has no successors, then  $L^{B}(\underline{I}) \otimes 1$ ; otherwise,  $L^{B}(\underline{\Gamma}) \otimes 1 \cdot \mathbf{max}$

2. Let  $L^{B}(T_{majr})$  represent the smallest integer such that  $L^{B}(T_{max}) \ge L^{8}$  ^ for all tasks  $T_{K}$ .

a If  $T_{\kappa}$  has ho predecessor, then  $L^{F}(T_{\kappa}) \ll L^{B}(T_{max})$ , otherwise,  $L^{F}(T_{\kappa}) \gg \min\{L^{K} \mid T_{V} a T-MM$ .

We present an intuitively obvious elementary theorem. Theorem. AM tasks  $T_E$  with L^^or L^] may be started in

parallel as independent tasks if all tasks T with L^T) - L V j + 1 [or  $L^F(Ty) \ll L^{\uparrow}T^{\uparrow} + 1$ ] have completed execution, without violating the precedence constraints imposed by  $G_A(V,E)$ .

The tasks  $T_x \in T$  are first assigned to processors  $P_e eP$  without regard to the resource constraints of  $R^A \in R$  and then scheduled on them taking into account the resource constraints. If resource constraints are violated, the starting time of the task is delayed untM sufficient amount of resources are released by tasks which have already been scheduled. The tasks in T are scheduled in the decreasing order of thair levels  $L^B(T)$ .

In order to understand how the scheduling procedure works it is convenient to assume that all tasks  $T_{\rm J}$  with L^T J > I have already been assigned to processors and scheduled on them. Consider the set • of

tasks T<sub>¥</sub> such that L<sup>B</sup>(T<sub>n</sub>) « I. Let • - { $J_{\%}$ ,  $T_n$ ,... T<sub>x</sub>. and define the set J - {1,2,...|+|} so that the elements & J are to lone to one correspondence with tasks in •. Let PI-{1,2... M} represent the set of processor indices to which tasks are to be assigned without regard to the resource requirements. This assignment problem may be formulated as an NP-complete integer linear program (ILP)

z<sup>^</sup> « 0 or 1. til icPl and all jeJ

Solution of ILP gives the optimal processor assignment that minimizes the latest finish time COMP TIME of the independent task set 4\*. z.»1 if  $T_K$  is assigned to processor 9, and  $z^*$  0. otherwise. ILP can be solved by a general ILP algorithm such as cutting- plana method or branch and bound but such solution procedures arc NP-complete. We solve ILP by transforming it to another problem ILP'.

ILP<sup>1</sup> is known as the Maximum Weighted Matching problem, y<sup>x</sup>'s have the same interpretation as z, <sup>f</sup>s. c, Js and b,'s are defined by me algorithm Assign Tasks. Solution to (ILP') yields an upper bound, UB, for the solution to (ILP). The inequality constraints and the objective function of »LP<sup>f</sup> are modified to improve UB and bring it closer to the solution of ILP.

## Alacrithm Airekin Tasks:

- 1. Initialize :  $b^M$ . for all iePI.  $t_{tj}$  ( $f_M$ ,  $t_{tj}$ ) ( $t_{tj}$ , for all icPI and jcJ.

- 2. Solve (ILP').

- 3. tp, Jj t<sub>1jyir</sub> for til iePl

- $i^* \bullet \{x \mid tp_K \land tp_t \text{ for all iePl}\}$

if (MTC is TRUE) Go to step 6.

if «ax (tp, >\_UB) Go to step 5.

4.

$$b_1 * |J|$$

for all isPI

**b.... ( $\Sigma$ .  $y_1 \cdot y_2$ ) - 1**

$$UB \ll tp / 4$$

60 to step 2.

$$b_{1} = \left( \frac{T}{2k_{1}} \quad y_{1} + \frac{1}{2} \right) - 1$$

MTC • TRUE

$$c_{1j} = \left\{ \left( \frac{T}{2k_{1}} \quad t_{1j} \right) \right\} / t_{1j} / \frac{T}{2k_{1}} \quad t_{1j} z_{1j}, \text{ all is PI and jeJ}.$$

Go to step 2.

6- <sup>™</sup> (tp,\* ⇒ US) go to step 7. Z<sub>11</sub> = Y<sub>11</sub> for a11 iePI. jeJ

UB<sub>f</sub> « tp<sub>f</sub>\*

----

Go to step 5.

<sup>7</sup>- \*Pi • fa ∗u <sup>i</sup>zu for all iePl

b<sub>i</sub> ■ <u>X</u> ≥<sub>1,1</sub> for all 1ePl.

COMP TINE - tPi

following 2 sets

- ^.Hz<sub>\*</sub> (output of algorithm assign task) is 1, task T<sub>&</sub> has been assigned to processor P<sub>i</sub>. For each jePl, form a set J = { i z<sub>µ</sub> = 1 } and a set - f T J z<sub>µ</sub> - for i = 1... J -1 } Set \* is a I \* of taskTkhat have been assigned to processor P<sub>i</sub> in increasing order of their total resource requirements.

- 2. For each set J<sub>jt</sub> iePl, tp<sub>t</sub> (output cf algorithm assign task) represents the total time taken on processor P<sub>1</sub> assuming ail tasks assigned to it could be executed on it in succession without violation of resource constraints. Form a set TP « {tPj # 0. for all icPlJtp; ≤ tp<sub>u</sub>, }. Note that the set TP may have fewer than n elements.

The tasks on a processor are scheduled in the increasing order of their total resource requirements. Let  $V^{\Lambda}_r$  ...  $r^*_L$ ] represent the total resource requirement of all tasks  $T_{\mu}$  such that  $L^{B}(Ty)-I+1$  or  $L^{F}(TJ-I)$  and task  $T_{\mu}$  has been scheduled. The remaining tasks are scheduled by the following algorithm:

## Algorithm Schedule Tasks

1. While TP is not empty perform the step

a. Lets » 1\* max {r(T<sub>x</sub>) • t<sub>D.</sub> JL<sup>B</sup>(T<sub>x</sub>) = 1\*1}

- b. For each v,  $1 \le v \le L$ ,  $l \in tr / * \pounds r^{k}$  where x is such that  $L^{B}(T_{X}) \gg U1$  or  $L^{8} \wedge -!$  and  $T_{x}$  has been **scheduled**.

- c. Let tp<sub>(</sub> be the first element in TP. While ¥ is not empty perform the step

i. let  $T_x$  be the first elementin<sup>\*</sup>.

it. if for each v. 1 < v < L,  $r_y' \cdot r^{-c}$  fiirj then let  $r(T_x) \cdot s$ , for each v, let  $r/J_r/ \cdot r^{-c}$  and remive  $T_x$  from  $\cdot r$  Task  $T_-$  is scheduled on processor  $P_r$  and  $X_{ta} \cdot s = 1$  for  $k \ll s + 1, \dots + t_{a}$ .

الجوالور المتحالجين والاروا والعار

d. Remove tp, from TP.

· · · · · · · · · · ·

- Form a set <\* of all tasks T<sub>y</sub> which have not been scheduled and have L<sup>^</sup>. )<sub>y</sub> = L

- a Repeat this step until + is empty. If for each v,  $1 \le v \le L$ ,  $r_y^* + r_{vy} \le 5(r^{a}$  and if for some i.t^^idte time of processor p,, then schedule T on P, and remove T from <> Else remove T from <>.

Each time a task which has been assigned cannot be scheduled because of insufficient resource, an entry is mad\*\* in a Resource Shortage Table indicating the particular task which could not be scheduled together with units of the particular resource/resources which were needed but were not available. Once all tasks T<sub>x</sub> with L<sup>B</sup>(T<sub>x</sub>) \* I have been scheduled, tasks T<sub>y</sub> with L<sup>B</sup>Oy » 14 are assigned to processors and then scheduled. The steps are repeated until all tasks T<sub>z</sub> with L<sup>8</sup> ^ » 1 have been scheduled. The specific details and the rules for breaking ties while forming the different sets are described in [43].

. . . . .