### NOTICE WARNING CONCERNING COPYRIGHT RESTRICTIONS:

The copyright law of the United States (title 17, U.S. Code) governs the making of photocopies or other reproductions of copyrighted material. Any copying of this document without permission of its author may be prohibited by law.

ASP: An Interactive APL Circuit Simulation Package

.

by

Gregory D. Jordan

DRC-01-08-82

April, 1982

# ASP;

# AN INTERACTIVE APL CIRCUIT SIMULATION PACKAGE

by Gregory D. Jordan

Submitted in partial fulfillment of the requirements for the degreee of Master of Science

**Department of Electrical Engineering**

**Carnegie-Mellon** University

August 19, 1981

## TABLE OF CONTENTS

| 1. INTRODUCTION                                   | 5   |

|---------------------------------------------------|-----|

| 2. THEORETICAL CONSIDERATIONS                     | 5   |

| 2.1 Modified Nodal Analysis                       | 5   |

| 2.2 The Development and Use of Some Simple Stamps | . 6 |

| 2.3 Stamps for Nonlinear Elements                 | 8   |

| 2.4 Stamps For Energy Storage Elements            | 10  |

| 2.5 Solving the Circuit Equations                 | 13  |

| 3. IMPLEMENTATION CONSIDERATIONS                  | 15  |

| 3.1 Help Files                                    | 15  |

| 3.2 Input Overview                                | 16  |

| 3.3 Nonlinear Elements                            | 17  |

| 3.4 Macros                                        | 19  |

| 3.5 Design Constraints                            | 20  |

| 3.6 Break Points                                  | 21  |

| 3.7 Interactive Checks                            | 22  |

| 4. DESIGN DECISIONS                               | 25  |

| 4.1 Flexibility vs. Interaction                   | 25  |

| 4.2 Run Time vs. Error Tolerances                 | 26  |

| Appendix A. Stamps                                | 29  |

| Appendix B. Function Level Description of ASP     | 35  |

| B.1 Mainstream Functions                          | 35  |

| B.2 Utility Functions                             | 39  |

| Appendix C. ASP User's Manual                     | 43  |

١

UNIVERSITY LIBRARIES CARNEGIE-MELLON UNIVERSITY PITTSBURGH, PENNSYLVANIA 15213

### Acknowledgements

Many thanks to my advisor Steve Director for his cuidance and advice during the past year.

2

í

÷.

I

÷

\$

### CHAPTER 1 INTRODUCTION

A circuit designer typically has many hardware and software design aids available for use. When doing hardware work, the designer builds small sub-circuits and tests each one separately before assembling the final project. To test these sub-circuits, signals may be entered so the designer can examine the sub-circuit as it is slowly stepped through its functions. At any point, the designer may wish to stop and change portions of the circuit to enhance performance.

Unfortunately, existing circuit simulators [Weeks 73],[Cohen 78] were not designed to be used in this manner. Present simulators can handle large circuits but allow very little interaction. Specifically, existing simulators cannot be halted during execution to make on-line changes to the circuitry. ASP was designed to fill this gap in circuit simulation technology.

This paper will describe the background and implementation of ASP, an <u>APL Simulation</u> <u>Package</u>. Initially, motivation for ASP will be discussed. The advantages and disadvantages of APL will then be mentioned to give the reader a better understanding of the features of ASP. Theory behind the algorithms used in the simulator will then be considered, followed by a review of some implementation considerations. Finally, some of the major design decisions made in ASP will be discussed and justified.

ASP was written to piovide APL users with a highly interactive circuit simulator with good on-line help features. The most obvious use for ASP involves circuit optimization work currently under development at Carnegie-Mellon University. The nature of optimization makes it imperative that a circuit simulator be available. While it is possible to manually derive circuit equations, this becomes very cumbersome for all but the simplest of circuits. ASP allows the developers to make more extensive tests of their circuit optimization algorithms.

APL was chosen for this type of work because of the following features:

- APL is a highly interactive language, that is, user input is very easily incorporated into programs. It is also quite simple to check input for syntax errors or to provide the user with access to global variables.

- It is very easy to develop new algorithms using APL. Once the language has been mastered, the programmer may take advantage of the many powerful operators available in APL to decrease development time.

- Debugging is very simple in APL due to the existence of commands such as TRACE and the availability of global variables.

ASP makes use of these positive aspects by performing interactive checks on user input, making on-line help available, and allowing the user much more control over the simulation than is normally possible.

Unfortunately, ASP is also constrained by the negative aspects of APL. Because APL has no compiler, execution times are relatively slow. To compensate, ASP has some special features which allow the user to exert more control over his/her usage of CPU time.

- ASP allows the user to determine error constraints. To reduce CPU time then, the user may choose to allow more truncation error.

- ASP allows the user to avoid needless dc simulations. Before a transient simulation is done, ASP must somehow determine the operating point of the circuit. If the user wishes, he/she may enter the operating point of the circuit and eliminate the dc simulation. If the operating point is unknown, ASP will solve for it.

- ASP allows the user to specify break points, or halting points during the circuit simulation. At each break point, the user has the option of changing break point data, changing circuit data, or simply continuing with the simulation.

Another negative aspect of APL concerns readability of code. Because of the abundance of operators, APL is a very difficult language to read. To alleviate this problem, ASP code contains many comments. Each function heading describes local and global variables used in the function. The heading also lists any functions which may be called during the execution of the present function. In addition, extensive comments have been written within the body of the function to enhance readability.

## CHAPTER 2 THEORETICAL CONSIDERATIONS

Before beginning a specific discussion of the features of ASP, this paper will first examine the theoretical issues which affect circuit simulation. In particular, the concept of modified nodal analysis will be reviewed. With this concept in mind, simple element stamps may be developed for use in the simulator. The idea of stamps can then be applied to more complex elements such as nonlinear elements, capacitors and inductors; however, algorithms to solve nonlinear equations and do numerical integration will be necessary. Finally, it is desirable to solve the resulting matrix equation in an efficient manner. This section will deal with all of the above issues and describe the algorithms used in ASP.

#### 2.1 Modified Nodal Analysis

The modified nodal method was developed as an alternative to the nodal and tableau methods. The major disadvantage of the tableau -approach was that it produced large numbers of equations and variables. The nodal method addressed this problem by making node voltages the basic variables. One disadvantage of the nodal method is that branch currents are not conveniently obtained as output A related problem is that voltage sources and some dependent sources are handled very inefficiently. To remedy these problems, Ho, Ruehli, and Brennan [Ho 75] proposed some modifications to the nodal method. The resulting method was then called the modified nodal analysis (MNA).

The basic premise of modified nodal analysis is that the basic variables are node voltages and the branch currents of voltage sources, inductors, and other elements whose currents are controlling variables. Introducing the extra basic variables allows voltage sources and dependent Sources to be handled much more efficiently than in nodal analysis. It also ^allows inductor currents to be easily accessible as output Because of these characteristics, modified nodal analysis is the method used in ASP.

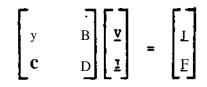

The MNA matrix can in general be expressed in the form:

where  $\underline{V}$  is the vector of node voltages,

1 is the vector of branch currents associated with voltage sources, inductors, and some dependent sources.

Y contains the partial derivatives of KCL equations with respect to the node voltages,

B contains the partial derivatives of KCL equations with respect to the branch currents,

C contains the partial derivatives of branch relationships with respect to the node voltages, and D contains the partial derivatives of branch relationships with respect to the branch currents.

J and P contain values of voltage sources and current sources. These two vectors may also contain contributions from nonlinear elements and energy storage elements.

2.2 The Development and Use of Some Simple Stamps

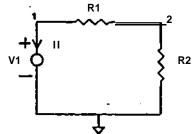

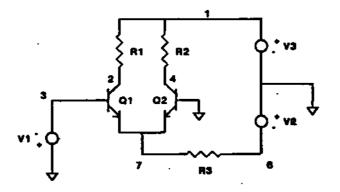

To further illustrate MNA, it will be useful to construct and solve a simple circuit using the modified nodal analysis approach. The simple circuit will consist of a voltage source and two resistors as shown below.

Usmc MNA. three equations are written to solve this circuit. Two of the equations will add the currents leaving each of the nodes. The third equation will specify the branch relation of the voltage source. The equations resulting from an MNA analysis of the circuit are:

1:

$$1 + (1/R)v - (1/R)v = 0$$

2:  $- (1/R)v + (1/R + 1/R)v = 0$

I:  $v = V$

or. in matrix fArm:

6

$$\begin{bmatrix} 1 & 1/R_{1} & -1/R_{1} \\ 0 & -1/R_{1} & 1/R_{1} + 1/R_{2} \\ 0 & 1 & 0 \\ \end{bmatrix} \begin{bmatrix} i_{1} \\ v_{1} \\ v_{2} \\ v_{2} \end{bmatrix} \begin{bmatrix} 0 \\ 0 \\ v_{1} \\ v_{2} \\ v_{3} \end{bmatrix}$$

Looking at the matrix equation, it can be seen that each element in the circuit contributes terms to the Jacobian. It may also be observed that the pattern of Jacobian terms is consistent within element types. For example a resistor between nodes M and R with a conductance of value G will contribute four terms to the Jacobian. (We are assuming, of course, that neither of the affected nodes are ground nodes.) This resistor will add two terms of G in the (M,M) and (N,M) positions of the Jacobian. In addition, two terms of -G will be added in the (M,N) and (N,M) positions. As a group, these terms which are added to the Jacobian for each element are called the element stamp. In the following two paragraphs, a closer look will be taken at resistor and voltage source stamps. For a complete listing of stamps used in ASP, see Appendix A.

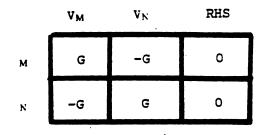

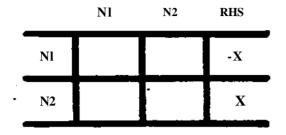

#### Resistor Stamp

Suppose a resistor connected between nodes M and N has a conductance of value G. This resistor will contribute a current to the equations of nodes M and N. The current leaving node M can be expressed as the difference of the node voltages M and N times the conductance G. A similar calculation can be done for the current leaving node N. The resulting effect on the MNA equations due to this resistor can then be expressed as:

In the stamp notation shown above, the rows are labeled with equation numbers and the columns are labeled with the voltage which the stamp terms in that column are multiplying. RHS indicates the right hand side terms. In addition, BR indicates a branch relationship.

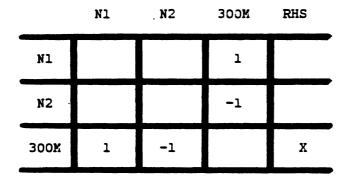

Voltage Source Stamp

7

Suppose a voltage source connected between nodes M and N has a value of Q volts. This voltage source has a branch current  $\langle IV \rangle$  which contributes current to the equations of nodes M and N. The voltage source value is then determined by its branch relationship equation. If the positive node of the voltage source is at node M, the resulting effect on the MNA equations can be expressed as:

|    | V <sub>M</sub> | VN  | IV  | RHS |

|----|----------------|-----|-----|-----|

| м  | 0              | b   | 1   | 0   |

| Ν. | 0              | 0   | - 1 | 0   |

| BR | • 1            | - I | 0   | Q   |

#### 2.3 Stamps for Nonlinear Elements

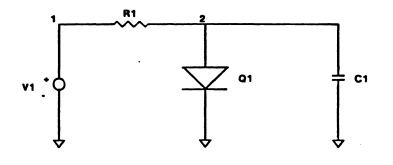

The concepts developed in the previous section can now be extended to nonlinear elements such as diodes and transistors. In this section, the development of a diode stamp will be discussed. The transistor stamp or the stamp for any nonlinear element can be derived using a similar approach.

Consider a diode with the branch relation:

$$\mathbf{I} = \mathbf{Isie}^{\mathbf{V}/\mathbf{V}} \cdot \mathbf{1} >$$

(2.1)

where  $V_{\overline{1}}$  is the thermal voltage and Is is the saturation current.

It is obvious that:

$$\frac{dl}{dV} \ll \frac{Ls}{V_{T}} e^{-T}$$

(2.2)

Now suppose initial guesses of Vo and Io are chosen. The problem *is* then to satisfy equation (2.1) given the constraints of the circuit An easy way to solve this equation would be to use a Taylor series approximation. Linearizing about the initial guess and truncating after<sup>v</sup> the first two terms yields:

$$I \ll Io \cdot \underline{Is} \begin{array}{c} Vo/V_{T} \\ c \\ V_{T} \end{array} \quad (V - Vo)$$

(2.3)

The new I and V found when this equation is solved with the circuit constraints are presumably closer to the real solution than Io and Vo were. Replacing the initial guess with I and V, one can repeat the procedure to get an even more accurate approximation. Using this iterative method with appropriate initial guesses. I and V will eventually converge to the true solution. This is the form of the Newton-Raphson method which is used in ASP.

Given this method, it is now possible to derive the form of a diode stamp. Note that there are three separate terms in the Taylor series equation. Two of the terms are dependent on Io and Vo and are therefore known. Ignoring the third term, it becomes apparent that the contribution to the circuit from the equation is a current source.

That is, in the equation.

ś

$$I * Io - Is Vo e <2.4$$

I is known since all the right hand side terms are known, A known current corresponds to a current source in the circuit.

The other term is dependent on the unknown diode voltage V.

$$I \ll \frac{V_0/V_T}{V_T}$$

(2.5)

I is an unknown in this equation and is dependent on V. An unknown current dependent on the voltage across the element corresponds to a conductance in the circuit.

Combining all of the terms in the Taylor series and converting the contribution of each term into a circuit element yields a stamp. The diode stamp can then be expressed as a current source of value equation (2.4) in parallel with the conductance indicated in equation (2.5). This stamp will be updated according to the Taylor series expansion after each new iteration of V and I is found. When the values begin to converge to the real solution, one can check the error criterion and stop iterating at the appropriate time.

#### 2.4 Stamps For Energy Storage Elements

ķ

Stamps are still unknown however, for energy storage elements, a class of elements which includes both capacitors and inductors. Since the branch relations for capacitors and inductors involve derivatives, a method for numerical integration must first be found. Numerical integration schemes make an approximation to the integral by taking small time steps and interpolating. The method used in the simulator was proposed by Van Bokhoven [Van Bokhoven 75] in a 1975 paper. Some changes have been made in order to simplify the algorithm and reduce the complexity of calculations.

The method is derived using Newton's divided-difference interpolation formula. This method makes predictions to new data using previous, data. Newton's interpolation formula truncated to two terms suggests that a new approximation to X can be made using:

$$X(t_{n^{*1}}) \ll X(t > \bullet (t_{n^{-1}} - t_{n^{-1}})X(t_{n^{-1}})$$

(2.6)

where t indicates the time of the last known value of X, t is the time previous to t,  $n^{-^{\wedge}}$

and X(t ,t ) is a divided-difference given by the formula:

$$\frac{X(t_{p} - X(l_{p-1}))}{t_{p-1}}$$

(2.7)

To simplify this equation, let us define some new variables.

$$\mathbf{h}_{\mathrm{I}} = \mathbf{t}_{\mathrm{n+1}} - \mathbf{t}_{\mathrm{n}}$$

$$\mathbf{h}_{\mathrm{1}}' = \mathbf{t}_{\mathrm{n}} - \mathbf{t}_{\mathrm{n-1}}$$

$$\mathbf{d}_{\mathrm{i}} = \mathbf{h}_{\mathrm{i}} / \mathbf{h}_{\mathrm{I}}'$$

٨

n n—1

Lei us also define the following conventions:

#### Х

represents the (M-l>st prediction of X at the <n+l)st time step and

X n-1

represents the final calculation of the value of X at the (n+l>st time step.

Equations (2.6) and (2.7> can then be rewritten as:

ŧ

$$\frac{-1}{X} \underset{n-1}{\overset{\times}{\times}} X_{n}$$

(2.8)

$$\frac{1}{X_{n^{*1}}} \ll \frac{1}{X_{n^{*M}}} + \frac{1}{4} (X_{n} - X_{n}^{-1})$$

(2.9)

Using the above equations, the simulator makes a zerotb **and** first order prediction to the value of X at the new time step. To correct this prediction, Van Bokhoven suggests an approach that is also based on Newton's divided-difference interpolation formula.

Corrections are made by approximating the derivative of X with respect to time. Using divided-differences, the derivative can be approximated by  $X(t_{n^{n''}}, t_{n-1})$ . A second order correction can be made using the formula:

$$\frac{dX}{dt} / n+1 = \frac{x_{n-1} - x_{n-1}^{-1}}{b_{1}} \ll \frac{x_{n-1} - x_{n+1}^{-2}}{b_{2}}$$

(2.10)

where  $h_2 = t_{n*l} - t_{n-l}$

Using these equations then, the stamp for a capacitor or inductor can be calculated. For example, suppose we have a circuit where the only unknown is a capacitor voltage. X. At each time step, zeroth and first order predictions of X would be made. Once these predictions are known, th? capacitor stamp can be temporarily added to the circuit in order to solve for the voltage at the present time step. The capacitor stamp consists of:

A current source of value:

(C/h)

$$X_{n^{*1}}^{-1}$$

\* (C/h)  $X_{n^{-1}}^{-2}$

in parallel with

a conductance of value: .

$$\cdot (C/hj)$$

where C is the value of the capacitor in farads.

The NfNA system of equations can now be solved for the final solution at the in+Dst time step.

Inductors can be handled in a similar fashion. The only major difference is that while

the capacitor stamp consists of a current source in parallel with a resistor, the inductor stamp consists of a voltage source in series with a resistor. This is very desirable since inductor currents are available as output because of the presence of a voltage source in the stamp.

The other portion of the Van Bokhoven algorithm is step size control. It is important that step sizes are well chosen for a number of reasons. If the step size is too small, the simulation will take a very long time. If the step size is too large, the numerical integration algorithm may not converge to the desired solution or truncation error may be too large. To minimize CPU time, it is necessary to choose the largest possible step size which satisfies the desired error criterion.

Using the remainder term from Newton's interpolation formula, second order truncation error at the nth step can be calculated using the formula:

$$\frac{1}{E_{n}^{3}} = \frac{1}{(X_{n}^{3} - X_{n})}$$

(2.11)

$$\frac{1}{1 + h_{3}B_{2}}$$

where

$$h_3 = t_{n+1} - t_{n-2}$$

$h_2' = t_n - t_{n-2}$

$B_2 = (1/h_1) + (1/h_2)$

$\frac{-3}{X_n} = \frac{-2}{X_n} + d_2 (X_n - \frac{-2}{X_n})$

and  $d_2 = d_1 (h_2/h_2')$

It is now possible to predict the second order truncation error at the (n+1)st step if a step size of h is used. Extrapolating from the above formula and making substitutions yields:

$$\frac{\overline{E}_{n+1}^{3}}{((1/h) + (1/(h+h_{1}))) + (1/h_{2})) \overline{E}_{n}^{2}}$$

(2.12)

If the predicted error is set equal to the maximum allowable error, the resulting nonlinear equation in h can then be solved using the Newton-Raphson technique. This new step size is then used to make the next prediction and correction by updating the stamps of energy storage elements. The circuit equations are then solved and a new error is determined. If the new error is greater than the maximum allowable error or if a nonlinear element stamp did not converge, the simulator rejects the step, cuts the step size in half, and starts the process again. If the new error is within tolerances, the simulator will increment time and solve for a new time step.

#### 2.5 Solving the Circuit Equations

Į

Finally, a technique is necessary to efficiently solve the matrix equations which have been created. Such a technique should take advantage of the special features of the circuit equation matrices:

- 1. Sparseness Large circuits especially have a relatively small proportion of nonzero elements. Hence the solution method should avoid storage of the zero-valued coefficients. The method should also avoid needless multiplications by zero.

- 2. Uniformity That is, the equations of each circuit have a particular pattern of zeroes and non-zeroes. In spite of updating stamps for energy storage and nonlinear elements, this pattern remains the same. A good method would take full advantage of this fact

One can take advantage of the sparseness and uniformity properties by using a\* combination of LU factorization and sparse matrix methods.

LU factorization involves factoring the matrix equation to be solved into an upper triangular(U) and a lower triangular\*L) matrix. Once these two matrices are known, a simple forward and backward substitution will solve the problem. Since the matrix is sparse however, many fewer operations need to be done than the total indicated by the substitutions.

The sparse matrix method used in ASP allows for efficient storage of the jacobian matrix. Three vectors are used to index and store members of the jacobian.

- JA is a vector containing column indices of all the elements

- 2A is a vector containing row pointers

- $\underline{A}$  is a vector containing the nonzero elements of the jacobian

After the three vectors are compiled, pivoting is done using the Markowitz criterion [Markowitz 57] to reduce fill and operation count.

LU factorization and sparse matrix techniques will not be discussed in greater detail in this paper. Further information on sparse matrix techniques can be found in <u>Sparse</u> <u>Matrices and Their Applications</u> [Gustavson 72]. These algorithms were packaged by Jim Christ and Fred Heaton as a semester project for 18-701. Because of the nature of the interface, the existence of sparse matrix techniques is nearly invisible to the simulator.

## CHAPTER 3 IMPLEMENTATION CONSIDERATIONS

This chapter will deal with specific implementation issues concerning ASP. Emphasis will be placed on interesting or new features of ASP. A better understanding of the organization and use of the simulator can be gained by reading this section and referring to the appendices at the appropriate times.

#### 3.1 Help Files

٩

The first unique feature of ASP is the set of twenty seven help files in the ASP workspace. Many of these help files summarize syntax for the different element types. Each time the user is prompted for input, it is possible to type HELP and receive some. In addition to the more specific help files, two general files exist which allow the user to see what type of help is available. The most general of these two files is listed below:

A LIST OF ALL HELP FILES AVAILABLE ALONG WITH THEIR SUBJECT IS:

HELP - THIS FUNCTION! HELPBKADD - ADDING BREAK POINTS HELPBKDROP - DROPPING BREAK POINTS HELPBKUTILS - RESPONDING TO UTILITIES MENU AFTER BREAK POINT HELPBREAK - SPECIFYING BREAK POINTS AT INITIAL INPUT HELPC - SFECIFYING CAPACITORS HELPCON - SPECIFYING DESIGN CONSTRAINTS HELPDEFN - DEFINING NONLINEAR MODELS HELPDEP - SPECIFYING DEPENDENT SOURCES HELPDROP - DROPPING ELEMENTS HELPGYRA - SPECIFYING GYRATORS HELPI - SPECIFYING CURRENT SOURCES HELPINP - LISTING OF ALL CIRCUIT ELEMENT INPUT HELP FILES HELPINPDEC - RESPONDING TO TYPE OF INPUT QUESTION HELPL - SPECIFYING INDUCTORS HELPMACRO - SPECIFYING MACROS HELPNODEOUT - SPECIFYING NODE VOLTAGES FOR OUTPUT HELPOUTFILE - WRITING TO EXTERNAL FILE HELPQ - SPECIFYING NONLINEAR ELEMENTS HELPR - SPECIFYING RESISTORS HELPREAD - HAVING FILE READ BY SIMULATOR HELPRINT - SPECIFYING PRINTING INFORMATION HELPSIM - CHOOSING TYPE OF SIMULATION HELPTRAN - SPECIFYING TRANSIENT SOURCES HELPUTILS - RESPONDING TO GENERAL UTILITIES MENU HELPV - SPECIFYING VOLTAGE SOURCES VCURSXPLAIN - SPECIFYING CODED CURRENT AND VOLTAGE NUMBERS

In case this on-line help is not sufficient, a more extensive source of help is the ASP User's Manual listed in Appendix C.

#### **3.2 Input Overview**

Before moving on to discussions of specific elements and features, the input language of ASP will be briefly reviewed. A line of element input is used to specify the following information:

- the element type

- the element number

- the nodes which the element is between

- and the value of the element or information to determine element definition.

Some typical element specifications would be:

Rl 1 2 1000 C2 39 50 1E.NG5

٩

VI 987 34 10

Other types of input are accepted by ASP as well. The user may choose to specify break points, design constraints or simulation time and printing information. These structures as well as a more comprehensive review of element specifications can be found in the ASP User's Manual which is Appendix C.

16

#### **3.3 Nonlinear Elements**

Another special feature of ASP is the flexibility it has with regard to nonlinear elements. The user may specify nearly any type of nonlinear element for ASP to process. The only restrictions are:

- 1. The user must be able to write equations to express each element current in terms of node voltages.

- 2. The user must be able to write equations to express the partial derivatives of each element current with respect to the involved node voltages.

Many well known models lend themselves easily to this format The Ebers-Moll transistor model and the simple diode model are especially useful and easy to specify. It is possible to specify many different models and to save these models in the workspace for future use. It is also possible for the user to specify a nonlinear element with as many nodes as necessary. There is no limit to number of terminals on an ASP nonlinear element.

We now *give* a thorough discussion of how nonlinear elements are handled in ASP. A nonlinear controlled source is specified in the input language by the statement\*

QK NI N2 . . . NN MODEL PI P2 . . . PM

- where Q signifies a nonlinear element

- M is the number of the nonlinear element.

- N1, N2, . . . NN are the nodes to which the nonlinear element is connected,

- MODEL is the name of the function which contains the model definition,

- and PI, P2, . . . PM are parameters to be used by the model function.

Before entering ASP, the user should have created the two defining functions and saved them in the ASP workspace. In our example, the function MODEL is specified so the two functions should have been called MODEL and DMODEL (The derivative function name should always correspond to the current function name preceded by a 'DM. MODEL specifies N-1 element currents in terms of the N node voltages. The Nth current can, of course, be determined from the first N-1 currents. DMODEL specifies the derivatives of each current with respect to each node voltage. That is MODEL returns an N-1 vector of currents and DMODEL returns a N-1 x N matrix of derivatives. Both of these two functions may accept and use the P parameters as part of the nonlinear model. Using these two functions and the user input shown above, ASP can accurately model the nonlinear element according to user specifications. In Chapter 2, it was shown that a diode can be modeled by a parallel combination of a resistor and a current source. It is possible to use this same technique with any nonlinear element. For example, suppose the equation of a nonlinear element can be expressed as:

$$i_{m} {}^{s} {}^{f} {}^{$$

If an initial guess of  $v_{10} \gg v_{,0} \ll \cdots = v_{NO}$  is chosen \*a Ta>rlor series expansion can be done to linearize the equation.

$$i_{m,l} = i_{m0} \cdot (di_{m0}/dv_{>(v_{-}v_{-})})$$

(3.2)

$$\cdot (di_{m0}/dv_{>(v_{-}v_{-})} \cdot ...)$$

$$\cdot (di_{m0}/dv_{-})(v_{-}v_{-}) \cdot ...$$

$$\cdot (di_{m0}/dv_{-})(v_{-}v_{-}) \cdot ...)$$

As before, it is possible to notice that there are two types of terms in the above equation. One type consists of all terms which must be calculated at the zeroth iteration. Because these terms are known, they effectively add a current source to the circuit The other type consists of terms which are dependent on the node voltages at the first iteration. Since these terms are unknown and relate the current to the node voltages, they effectively add a resistance to the circuit. In this way, the stamp for a nonlinear element can be determined. MODEL and DMODEL calculate all the necessary terms to add the stamp to the jacobian. After each iteration, the stamp is updated until the solution converges.

The function NEWRAP is used to implement the Newton-Raphson iteration in ASP. The first function to be called by NEWRAP is NOOSAVE. This function saves the elements of the jacobian which will be altered by any nonlinear stamp. NOOSAVE is necessary so the jacobian can then be restored after the iteration calculation is done. UPDATQ is then called to update the nonlinear stamp. UPDATO calls the model function and the derivative function, creates the stamp, and adds it to the jacobian. The matrix equation is then solved and the difference between the new solution and the solution from the previous iteration is measured. The maximum voltage and current errors are found and these are compared with an absolute and relative voltage and current error. If either error is too large. NOQRESTOR is called to restore the jacobian and another iteration is done. If the error is tolerable, NOQRESTOR is called, time is updated, and the simulator can then take another step. A function level description of ASP can be seen in Appendix B.

As the user specifies nonlinear elements, checks are run to ensure that input language syntax has been followed. ASP also checks that the necessary functions have been defined. No checks are done on the model definition function because of the great flexibility which the user has. The user must be careful to define the correct number of currents and derivatives and the user is responsible for the accuracy of the functions. It is anticipated that a user will only need to develop a few nonlinear models and can then store these models in his/her ASP workspace.

#### 3.4 Macros

To augment the extensive nonlinear element capability, ASP also allows the user to define macros or groups of elements. Macros become significant when the user needs to expand models to include energy storage elements. Since no capacitors or inductors can be expressed in a nonlinear model, macros are necessary to allow more sophisticated modeling. It is anticipated that any complex transistor models will be expressed as macros consisting of some nonlinear elements and some capacitors and resistors.

The specification of a macro is done by the statement:

MACM N1 N2 . . . NN ELEMENTS P1 P2 . . . PM

- where MAC signifies a macro,

- M is the element number of the macro,

- N1, N2, . . . NN are external nodes to which the macro is connected,

- ELEMENTS is the name of the function which defines the macro elements,

- and P1, P2, . . . PT are the parameters of the macro elements.

Previously, the user should have created the function (ELEMENTS in this case) which contains the elements of the macro. The syntax for listing macro elements is only slightly different than the regular element specification syntax. Function definition and macro input are discussed in more detail in the ASP User's Manual.

When specifying a macro, ASP allows the user to specify parameters, and internal and external nodes for the macro. Parameters can be specified as VAL[1], VAL[2], ... VAL[M] corresponding to P1, P2, ... PM. Parameter passing allows the same macro to be used for many elements of the same form but with different specs. Internal nodes are specified as (INTERNAL), (INTERNAL+1), etc. ASP uses numbers greater than 7000 to refer to internal nodes. For more information on node and current syntax, see

Appendix I of the User's Manual. Elements of the macro refer to internal nodes in the above manner. After each macro *is* added to the data base, the global variable INTERNAL is updated so it is greater than the highest node specified thus far. This allows the user to specify internal nodes without any knowledge of which numbers have been used. As long as the user specifies nodes greater than INTERNAL, there should be no problem. External nodes are specified as <EXTERNAL[1]), (EXTERNAL[2]>, . . . (EXTERNAL[N]> corresponding to N1, N2, . . . NN. Specifying external nodes in this manner allows the macro to be interchangeable. The user can of course specify a node directly however this seems to defeat the purpose of macros.

Macros are implemented in ASP through the function ADMAC. This function looks at the user-defined ELEMENTS function and assigns numerical values to the variables EXTERNAL, INTERNAL, and VAL. ADMAC then pieces together these values and forms a character string which is of the same format as the regular element specifications. Finally, ADMAC calls the function CHANGE which calls the appropriate function to add the specific element.

• Very few checks are done on macros. The input specification *is* checked for duplicate elements and a minimal number of external nodes. A check is also run to make sure the function containing the macro elements exists. No checks are run on this ELEMENTS function so the user must be careful.

#### 3.5 Design Constraints

Since it is expected that ASP will be used as a design tool, a capability to evaluate design constraints has been included. Specifically, ASP can evaluate any function of the form:

$$\frac{1}{\mathbf{I}} = \prod_{\mathbf{f}} \frac{\mathbf{f}(\mathbf{y}, \mathbf{I})}{\mathbf{f}(\mathbf{y}, \mathbf{I})} dt$$

(3.3)

where f is a function of the node voltages  $\underline{V}$  and the branch currents  $\underline{h}$  and T is the ending time of the simulation.

- To specify a design constraint, the user types in: CONK CONFUNC

- where CON signifies a design constraint,

- M is the number of the constraint.

• and CONFUNC is the name of the design constraint function.

To define the function CONFUNC, the user must once again be familiar with the node and current syntax found in Appendix I of the User's Manual. CONFUNC should be a function of node voltages and branch currents and should return the value of the design constraint

ASP treats design constraint evaluation as a current source of value CONFUNC charging a capacitor of value IF. Using the numerical integration scheme mentioned in Chapter 2, it is possible to model the capacitor as a current source in parallel with a resistor. Design constraint evaluation then reduces to the problem of analyzing a circuit with two current sources in parallel with a resistor. ASP solves this simple circuit and returns the results of the function integration.

CONFUNC is defined with the aid of the ASP function NUM. This function takes the number of a node voltage or branch current and returns the present value of this voltage or current NUM allows the user to conveniently specify values of voltages and currents as opposed to names. CONFUNC then returns the value of the current source to be used in the circuit explained above.

Function evaluation is done in parallel with solution of the main circuit After a step is accepted, first and second order predictions are made to the value of the design constraint. The correction is then done as explained above. The user need not specify the design constraint as output since it will automatically be shown if constraints have been specified.

Once again, no checks are done on the user-defined function. The user must be careful to specify the proper voltages and currents and to return the proper value of the design constraint function. The user is reminded, however, if the specified constraint function does not exist

#### **3.6 Break Points**

i

Another special feature of ASP is its ability to process break points. Break points are user-specified halting points in the simulation. They are useful when the user can determine the success or failure of his/her test case before the simulation has finished. The user may wish to change the value of one element and then simulate the same circuit again. Break points facilitate manipulations such as this. Break points are specified by the input line:

BREAK T1 T2 . . . TN

Break point times need not be specified in ascending order however, they will be serviced in ascending order.

When ASP reaches the initial break point, voltages and currents will be calculated as usual and the break point utilities menu will be called. This menu gives the user seven options.

- 1. Add break points The user may add new break points to the present list. This capability is useful if the user would like to continue the unbroken simulation for some time longer than expected.

- 2. Delete break points The user may delete break points from the list. This is useful if the user decides that the simulation is running well and no more break points are necessary.

- 3. Examine break points The user may examine all break points specified so far.

- 4. Examine values of constraints, voltages or currents The user may examine the current status of any constraints, voltages, or currents.

- 5. Change circuit element data The user may temporarily return to the main utilities menu to add or drop circuit elements. This capability is useful if the user would like to change one or two circuit elements while keeping the rest of the circuit the same. After these modifications are done, ASP attempts to . use the old dc solution for the new circuit. In the case of minor circuit modifications, this would save the user a substantial amount of time. If the attempt fails, ASP solves for the new operating point.

- 6. Continue with simulation The user may continue with the simulation as if the break point was never serviced.

- 7. Exit Finally, the user may simply choose to exit from ASP.

#### 3.7 Interactive Checks

The final special feature of ASP to be considered is interactive checking. During the input phase, the user has the option of choosing interactive input or file reading input. If the user chooses to input circuit data interactively, each element specification will be examined for syntax errors. Appropriate error messages will be displayed and the user can make immédiate corrections and reenter the elements. In the case of file reading input, the user will see a list of errors. The user then has the option of entering the interactive input mode to make corrections.

Element specifications are checked for:

• omission of element numbers

i

- unacceptable characters (alpha or numeric)

- incorrect number of nodes specified

- shorted element specified

- node numbers or element number greater than 999

- non-integer node numbers

•

• and the existence of duplicate elements.

In addition, more specific checks are made on some elements. For example, a check is run to detect O-valued resistors. More extensive checks are also run on transient source information.

A more general checking function is also included in ASP. The function HANGELCK checks for hanging nodes, omission of simulation type information, omission of end time and printing increment information, failure to specify any elements, and failure to define a specified design constraint HANGELCK must be successfully completed before a simulation can be run.

## CHAPTER 4 DESIGN DECISIONS

One of the most difficult problems encountered while programming ASP involved the resolution of two important design decisions. To discuss these decisions, one must first understand some of the problem constraints. One of the major advantages of ASP was to be its interactive nature and the extent to which the user's input was checked for errors. In conflict with this goal was the necessity to make ASP a flexible and useful tool as well. The second trade-off involved simulation time and truncation error. In order to run a fast simulation, one must relax the error constraints. In order to run an accurate simulation then, one must be willing to sacrifice somewhat in the area of CPU time. In this chapter, these irade-offs will be discussed and the ASP project will be summarized.

#### 4.1 Flexibility vs. Interaction

ł

Two of the main areas where the flexibility vs. interaction conflict -came into focus - were the definition of nonlinear elements and the definition of macros. For nonlinear elements, it would have been possible to define one or two often used nonlinear elements as part of the package. Although the user would be confined to using these predefined models, he/she could be assured of correct syntax. Macros would not be allowed due to the difficulties involved with syntax checking. ASP chooses the alternate option of flexibility. The main reason for this choice is that the user is free to define <u>any</u> type of nonlinear element/macro combination. The user is not at all limited by predefined models or element types. In addition, macros can be used to define blocks of elements which may be redundant in a circuit, thus saving the user input time.

The cost of these advantages was seen as very minimal. The use of parameter passing in macros and nonlinear elements increases the flexibility of each model. Workspaces in APL also allow for easy storage of old models. Definition procedure was also simplified so that a user with some basic familiarity with APL should have very little trouble defining models.. Any initial difficulties the user may have seem insignificant when one views model definition as essentially adding a new, more exact element to the simulator's capability. Extensive syntax checking is done when any other element is entered by the user. These checks are listed in the User's Manual following the specific element syntax. The only known way for the user to be unexpectedly expelled from the simulation package is when the user incorrectly defines nonlinear models or macros.

#### 4.2 Run Time vs. Error Tolerances

٢

ł

The other important trade-off involves run time and error tolerances. ASP has a step size control mechanism which ties step size to truncation error. If the user is willing to allow large amounts of error, ASP will take relatively large steps. Conversely, if the user will not tolerate much error, ASP will take relatively small steps. Because APL has no compiler, run times can sometimes become excessively long if a tight error criterion is specified.

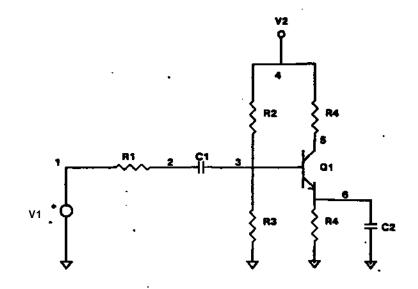

To illustrate the relationship between truncation error and step size, a dc simulation test case was run using three different error tolerances. The data below shows the effect which error tolerances have on CPU time.

Trial 1: V(3) = -0.1EVABS = .0001EVREL = .001V(2) = 9.922115064EIABS = 1E.NG7EIREL = .001V(1) = 10CPU time = 14:05 (in minutes:seconds) V(4) = 5.75843106Operation count = 1919006 V(6) = -10Statement ccunt = 550272 V(7) = -0.4014731114I(3001) = 1.714295548E-5I(3002) = -0.009598526889

I(3003) = -0.008638907752

26

Trial 2: V(3) = -0.1EVABS = .001EVREL = .01- V(2) = 9.922115064EIABS = 1E.N66EIREL = .01V(1) = 10CPU time = 6:30 (in minutes:seconds) V(4) = 5.758431061Operation count = 969950 V(6) = -10Statement count = 278226 V(7) = -0.40147311231(3001) = 1.714295548E-51(3002) = -0.009598526888K30Q3) = -0.008638907751

| Trial 3:<br>EVABS = .01                    |                      | V(3) = -0.1               |

|--------------------------------------------|----------------------|---------------------------|

| EVREL = .1<br>EIABS = 1E.NG5<br>EIREL = .1 |                      | V(2) = 9.922115122        |

|                                            | (in minutes:seconds) | V(1) = 10                 |

| Operation count                            |                      | V(4) = 5.75843422         |

| Statement count :                          | = 195558             | V(6) = -10                |

|                                            | · .                  | V(7) = -0.4014802619      |

|                                            |                      | 1(3001) = 1.714294262E-5  |

|                                            |                      | 1(3002) = -0.009598519738 |

|                                            | -                    | 1(3003) = -0.008638901316 |

The above data indicates a small correlation between error and correctness of the solution however, this will not always be the case. Obviously, for this circuit and similar circuits, the user should use a relatively lenient set of error parameters. For more complex circuits though, especially those with many energy storage elements, the user will probably want to enforce a tighter error constraint.

The correlation between CPU time and allowable error makes it clear that the user will want to choose the most lenient constraints possible which still yield useful results. It is also clear that even with lenient constraints, CPU times are very substantial. ASP

27

Í

alleviates this problem by giving the user enough flexibility to eliminate all unnecessary simulation time and error constraints. The user can choose his/her own error tolerances simply by setting the global variables EVREL, EVABS, EIREL, and EIABS in the ASP These variables correspond to the allowable relative and absolute voltage and function. current errors. ASP also eliminates any unnecessary dc simulations by prompting the user for the operating point before a transient simulation. The user can either specify the operating point or ask ASP to determine it. If the user can specify the operating point, the CPU time necessary for a dc simulation can be applied to more constructive problems. In addition, ASP allows the user to specify break points to eliminate unnecessary simulation time. The user can then continue or stop the simulation dependent on the previous results. Finally, after a break point has been reached, the user has the option of easily changing circuit data. If only minor changes have been made, ASF will iterate to the new operating point without ramping the independent sources. This will also save a considerable amount of CPU time.

ASP then was created as a relatively efficient simulator in a slow APL environment. Many features have been added to increase the productivity of the simulator and to eliminate unnecessary CPU usage. It is hoped that the combination of these features with the interactive checking and on-line help will make ASP a useful tool.

### APPENDIX A STAMPS

#### Current Controlled Current Source Stamp

CCCSM N1 N2 N3 N4 X

٢

1

|      | וא | N2 | NЗ | N4 | 100M | RHS |

|------|----|----|----|----|------|-----|

| Nl   |    |    |    |    | · x  |     |

| N2   |    |    |    |    | -X   |     |

| NЗ   |    |    |    |    | 1    |     |

| N4   |    |    |    |    | -1   |     |

| 100M |    |    | l  | -1 |      |     |

In the above stamp syntax, N1...N4 indicate nodes, 100M indicates a CCCS current in the ASP syntax, and RHS indicates the right hand side terms.

29

Current Controlled Voltage Source Stamp

CCVSM NI N2 N3 N4 X

|      | NI | N2 | N3 | N4 | 200M | 200M | RHS |

|------|----|----|----|----|------|------|-----|

| NI   |    |    |    |    | Л    |      |     |

| K2   |    |    |    | -  | -1   |      |     |

| N3   |    |    |    |    |      | -1   |     |

| N4   |    |    |    |    |      | -1   |     |

| 200K | 1  | -1 |    |    |      | *-X  |     |

| 200K |    | -  | 1  | -1 |      |      |     |

Capacitor Stamp in Element Form

CK N1 N2 X

The second order stamp for a capacitor of this form is:

a current source of value

(X%H[1])#(1st order prediction of capacitor voltage)

+ (X%H[2])#(2nd order prediction of capacitor voltage)

in parallel with

a conductance of value (X%H[1])+(X%H[2]) Inductor Stamp in Element Form

LK NI N2 X

The second order stamp for an inductor of this form is:

a voltage source of value (X%H[1])#(1st order prediction of inductor current)

• (X%K[2})#(2nd order prediction of inductor current)

in series with

a conductance of value (X%H[1])+(X%H[2])

Gyrator stamp

Ň

GYRAK NI N2 N3 N4 X

|    | Nl | N2 | N3 | N4 . | RHS |

|----|----|----|----|------|-----|

| NI |    |    | X  | -X   |     |

| N2 |    |    | -X | X    |     |

| N3 | -X | X  |    |      |     |

| N4 | X  | -X |    |      |     |

**Current Source Stamp**

IK NI N2 X

### **Resistor Stamp**

٩

RM NI N2 X

ţ

ţ

|     | NI   | N2   | RHS |

|-----|------|------|-----|

| NI  | 1%X  | -1%X |     |

| N2. | -1%X | i%>: |     |

÷

Voltage Source Stamp

VM N1 N2 X

ŧ

.

í

**1** - -

### Voltage Controlled Current Source

•

VCCSM N1 N2 N3 N4 X

۲

|      | Nl | N2 | N3 | N4 | RHS |

|------|----|----|----|----|-----|

| וא   |    | ·  | X  | -X |     |

| N2   |    |    | -X | X  |     |

| N3 · |    |    |    |    |     |

| N4   |    |    |    |    |     |

.

٠

# Voltage Controlled Voltage Source

VCVSM NI N2 N3 N4 X

ŧ

ť

¢

| <u> </u> | NI | N2 | N3 | N4 | 400H | RHS |

|----------|----|----|----|----|------|-----|

| NI       |    | -  |    |    | 1    |     |

| N2       |    |    |    |    | -1   | ·   |

| N3       |    |    |    |    |      |     |

| N4       | •  |    |    |    |      |     |

| 400M     | 1  | -1 | -X | X  |      |     |

# · APPENDIX B FUNCTION LEVEL DESCRIPTION OF ASP

In order to facilitate modifications to ASP and to enhance the readability of the APL code, the following function level description has been written. Functions will be grouped according to functionality and each group will be briefly described.

#### **B.1 Mainstream** Functions

ί

ASP The introductory function. ASF initializes variables\* and asks the user for his input type choice. ASP then calls one of the INPUT functions. INPUT The INPUT functions allow the user to input circuit INPUT functions are: INTERINP and FILEREAD. data. INPUT functions set MODE to <sup>f</sup>add<sup>f</sup> and call the CHANGE function. \* \* \* \* • \* \* \* \* \* \* \* \* \* CHANGE The CHANGE function decides what type of element the user is trying to specify. CHANGE then calls the pro- \* per CHECKING function. \*\*\*\*\* CHECKING The CHECKING functions check element specifications \* for proper syntax. CHECKING functions are: TWOCHECK, \* FOURCHECK, QCHECK, TRANCHECK, CONCHECK, PRNTCHECK, \* BREAKCHECK, and MACHECK. If proper syntax has not \* been followed, the user will be given an error message \*

\* and the INPUT function will attempt to read the next \* line. If proper syntax has been followed, CHANGE will \* \* call the appropriate ADD function. \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* ADD The ADD functions add element stamps to the jacobian \* \* \* matrix. ADD functions are: ADVCVS, ADVCCS, ADV, \* ADCCVS, ADCCCS, ADI, ADRES, ADGYR, ADQ, ADCL, and \* ADMAC. Some of the simple element additions are \* handled in the CHECKING functions. After the ADD \* functions are finished, the INPUT functions attempt to \* \* read the next line of input. \*\*\*\*\*\*\*\*\* If there is input on the next line, CHANGE is called and the process repeats until all input has been entered. Once this occurs, the UTILITIES function takes over. UTILITIES The UTILITIES function allows the user to choose one \* \* of the following seven options: Option 1 - Add more circuit elements. UTILITIES calls INTERINP and the user can add \* elements as before. Option 2 - Delete some existing elements. UTILITIES calls the function DROP. This function sets MODE to 'drop' and calls the CHANGE function. The CHANGE function then calls the proper DELETE function. DELETE functions drop element stamps from the jacobian matrix. DELETE functions are: DPVCVS, DPVCCS, DPV, DPCCVS, DPCCCS, DPI, DPRES, DPGYR, DPQ, DPCL, DPTRAN, DPMAC, DPCON and DPBREAK. Option 3 - Examine the input to date. UTILITIES exhibits the variable INP which contains all user input to date. Option 4 - Write the input to an external file. UTILITIES calls the function OUTFILE which allows the user to write the input to an external file.

Option 5 - Continue processing. UTILITIES calls the SETSIM function (see below) to set up the simulation. Option 6 - Exit Leave the ASP package. Option 7 - Return to breakpoint menu if applicable. The user will return to a previous menu if possible. \*\*\*\*\*\*\*\*\*\*\*\* + SETSIM SETSIM does the following to prepare for simulation: - Calls the function HANGELCK to check if all necessary information has been specified. HANGELCK also checks for hanging nodes in the circuit. - Calls the SEGREGATE function to distinguish between node voltages and branch currents. This is done to allow-separate criteria for voltage and current error. - Calls the PIVOT function which is part of the sparse matrix package. PIVOT pivots the jacobian to reduce fill. - In the case of a transient analysis, the user is prompted for the operating point. If it is \* known, a dc analysis can be eliminated. If the operating point is unknown, ASP solves for \* it using the DCSIM function. (Note: If a dc analysis is being done, DCSIM will be called. DCSIM is also called in case of an unknown operating point. DCSIM is not called when a transient analysis is being done and the operating point of the circuit is known to the user.) \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \*\*\*\*\*\*\*\*\*\*\*\* DCSIK DCSIM is the function called to provide a dc Simula- \* \* tion. DCSIM transforms each constant source into a \* transient source which reaches its value at time=.ls. \* Each transient source is then transformed into a tran- \* \* sient source which reaches its 0 value at time=.ls. \* That is each source is ramped up to its 0 value over a \* \* .Is interval. Each of the 'transient<sup>1</sup> sources begins \* with a value of 0. The solution of the circuit is \* obvious at- this point. By taking small time steps and \*

\* doing an evaluation at each point, the dc solution can \* \* be found. DCSIM sets up this transient simulation \* and calls TRANSIK to implement it. After the dc \* solution is found, TRANSIM may be called. + (Note: If only a dc simulation is being done, ASP stops at this point. Continue for more on transient simulations.) OUTASK is called here to ask the user which voltages or currents should be printed. TRANSIK TRANSIK does the following to implement a transient simulation: - Initialize variables necessary for simulation. - Call the STARTUP function to start off the simulation. STARTUP essentially does three first order corrections while the error estimation facility is being initialized. STARTUP initially calls the NOCLSAVE function which saves the values of positions in the jacobian which are affected by capacitors and inductors. - BEGIN the LOOP Reset variables. Call UPDATRAN to update transient source stamps. Call PRED to predict using the Van Bokhoven algorithm described in Chapter 2. Call CORRECT to correct using the Van Bokhoven algorithm from Chapter 2. Call NEWRAF to implement the Newton-Raphson algorithm. NEWHAP calls NOQSAVE to save values of positions in the jacobian which are affected by nonlinear elements. A loop is \* then begun: ..... NOQRESTOR is called tc restore the jacobian to its pre-stamp condition. UPDATQ is called to update the nonlinear stamp. GAUS is called to do the LU factorization. BACK and FOR are called to do backward and. forward, substitution. Error is then checked to see if \*

the iterations should continue. If not, NOORESTOR is called again to restore the jacobian. Error is checked to see if the step should be accepted or rejected. If the step is rejected, cut the step in half, restore the jacobian to its original condition and return to the beginning of the loop. If the step is accepted, Τk continue with: Restore each transient current source Tk With TRANIRESTOR. Τk Τk Evaluate the design constraint if nec-Tle essary. Increment time and restore the jacobian using NOCLRESTOR. Accommodate any printing requests or break point requests. Calculate a proposed step size using HCALC and continue the loop until the end time is reached. -----

**B.2 Utility Functions**

In addition to the functions already mentioned, there are other Utility functions in ASP. These functions handle small tasks which are necessary for the Mainstream functions to work effectively. A list of these functions and a small discussion on each will now be given.

- ASSIGN taxes the user-specified nodes and converts them into node numbers which the simulator can user ie. consecutive numbers.

- BKPNTADD prompts the user for break points to be added. This function is called from BKPNTUTILS.

- BKPNTDROP prompts the user for break points to be dropped. This function is also called from BKPNTUTILS.

- BKPNTUTILS gives the user options to change break point data, change circuit element data, or continue with simulation.

- CAPV determines voltage across two nodes for a given order of prediction.

39

COMPACT - drops unused nodes from consideration.

CREATE - is called by PIVOT to create temporary fill elements, (SPARSE MATRIX FUNCTION)

- DESTROY destroys positions in the jacobian. (SPARSE MATRIX FUNCTION)

- EXAMINE allows the user to examine present values of design constraints, voltages, or currents. This function is called from BKPNTUTILS.

- FASTADI adds a current source for a capacitor stamp.

- FASTADRES adds a resistor for a capacitor or inductor stamp.

- FINDINP finds total element information when given type and number of element.

- FN3EVAL evaluates the objective function at a given time.

- FPWL returns value of PWL function when given time and parameters.

- FSIN returns value of SIN function when given time and parameters.

- FUNCK checks if a given function exists in the workspace.

- INCR increments values of elements of the jacobian. (SPARSE MATRIX FUNCTION)

- IKIT initializes variables. (SPARSE MATRIX FUNCTION)

- LOOKUP looks up elements in the jacobian when given row and column indices. (SPARSE MATRIX FUNCTION)

- \*HUK returns current value of the given voltage or current.

PRINT - prints out the ASP workspace.

PUT - puts a given value into a specified row and column in the jacobian.

(SPARSE MATRIX FUNCTION)

PWLCK - checks the PWL portion of a PWL transient source.

REDUCE - removes a row and column pair from the jacobian. (SPARSE MATRIX FUNCTION)

ROW - calculates a given row of the LU factorization. v (SPARSE MATRIX FUNCTION)

\*SINCK - checks the SIN portion of a SIN transient source. TRANSBACK - does the back substitution for the transposed jacobian problem. (SPARSE MATRIX FUNCTION)

TRANSFOR - does the forward substitution for the transposed jacobian problem. (SPARSE MATRIX FUNCTION)

TRANSOL - solves the transpose problem. (SPARSE MATRIX FUNCTION)

TRANSPOSE - obtains column-wise representation of pivoted L and U matrices. (SPARSE MATRIX FUNCTION)

This list does omit all of the HELP functions which were previously listed. HELP files all begin with the letters 'HELP'.

# APPENDIX C ASP USER S<sup>#</sup>MANUAL

{

# ASP

# APL SIMULATION PACKAGE

A User's Manual

ASP is a simulation package written in APL by

ţ

٢

Gregory D. Jordan

# TABLE OF CONTENTS

÷

| 1. Introduction                                                 | 1      |

|-----------------------------------------------------------------|--------|

| 2. Getting Started                                              | 2      |

| 3. Input Syntax                                                 | 3      |

| 3.1. Resistors                                                  | 4      |

| 3.2. Capacitors and Inductors                                   | 4      |

| 3.3. Gyrators                                                   | 4      |

| 3.4. Linear Current Controlled Current Sources                  | 5      |

| 3.5. Linear Current Controlled Voltage Sources                  | 6      |

| 3.6. Linear Voltage Controlled Current Sources                  | • 6    |

| 3.7. Linear Voltage Controlled Voltage Sources                  | 7      |

| 3.8. Constant Voltage Sources<br>3.9. Constant Current Sources  | 8<br>8 |

| 3.10. Transient Voltage Sources                                 | 8<br>9 |

| <b>3.11.</b> Transient Current Sources •                        | 9      |

| 3.11.1. Allowable Types                                         | 10     |

| 3.12. Nonlinear Elements                                        | 10     |

| 3.12.1. Model Definition                                        | li     |

| 3.13. Macros                                                    | 12     |

| 3.13.1. Macro Definition                                        | 13     |

| 4. Necessary Input                                              | 14     |

| 4.1. DC Analysis                                                | 14     |

| 4.2. Transient analysis                                         | 14     |

| 5. Optional Input                                               | 15     |

| 5.1. Break Point Specification                                  | 15     |

| 5.2. Design Constraints .                                       | 15     |

| 5.2.1. Function Definition                                      | 16     |

| Appendix I. Explanation of Voltage and Current Numbering System | 17     |

| Appendix II. Test Cases                                         | IS     |

# **1. INTRODUCTION**

ŧ

This manual *is* intended for use with ASP which is now implemented on the CMU TOPSC system. A large amount of on-line help is available, however this manual is in most cases a more extensive source of information. Some knowledge of APL is valuable if the user would like to explore all of the capabilities of ASP. As a general tool, however, ASP can be used and enjoyed by everyone.

## **2 GETTING STARTED**

Before loading the ASP workspace, be sure to increase the allowable workspace size by typing: )MAXCORE 200

Next, to enter the simulator package, type:

)LOAD ASP ASP

The user will now be asked to input data. There are two possible input methods. The user may wish to copy data from a previously created external file or the user may wish to input data interactively. The syntax for each element remains the same in both cases. The user will probably want to use interactive input until he/she is familiar with ASP syntax. When naming external files for ASP to read, it is important to keep file names shorter than 8 characters or else an error will result.

## **3. INPUT SYNTAX**

In this section, each type of element will be examined and input syntax will be discussed. Some general points should be made first.

1. Error tolerances can be set by the user by altering the variables EVREL. EVABS, EIREL, and EIABS in the ASP function. These variables are the relative and absolute error allowable for voltages and currents. That is, the simulator checks that the maximum voltage error at each time step is less than:

# EVABS + EVREL#(the voltage which corresponds to the largest voltage error term)

A similar calculation is done for current error.

- 2. Scientific notation is acceptable to ASP, however abbreviations are not. That is 1E3 and 1E.NG12 are acceptable, however 1K and 1M are not. When using a TTY terminal, you will not be able to specify any macro element parameters or values less than .0001. In short, this occurs because TTYs convert the (.NG) character to the totally different (-) character. To avoid this problem, either switch to an APL terminal or use individually specified elements rather than macros.

- 3. Node numbers and element numbers must be positive integers less than 1000. The ground node must be labeled node 0. This is due to an ASP convention for handling internal nodes and currents. No hardship should result since ASP is not designed to handle hundreds of nodes or elements.

- 4. An acceptable input file consists of circuit elements and a DC or TRANSIENT line to indicate dc or transient simulation. If transient simulation is chosen, the user must also specify a PRINT statement. In addition, the user has the option of specifying break points using a BREAK statement or design constraints using the CON statement.

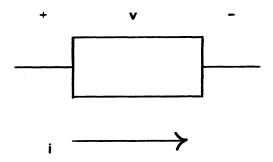

- 5. ASP uses the following convention for defining elements:

That is, current always flows from the positive to the negative terminal of an element. In addition, the ASP convention is that the positive terminal is always defined first. Be especially careful of this when defining current sources.

3

#### 3.1. Resistors

The basic form of resistor input is: RMN1 N2 VALUE

- where R signifies resistor,

- M is the number of the resistor,

- N1 and N2 are the nodes which the resistor is between,

- and VALUE is the value of the resistor in ohms.

Typical resistor specifications are:

Rl 1 2 10000 R50 67 734 200

Checks are run for 0-valued resistors, unacceptable alpha characters, node or element numbers which are not integers or are out of bounds, incorrect number of nodes entered, shorted elements, and duplicate elements, where duplicate means two resistors with the same element number.

#### **3.2.** Capacitors and Inductors

The basic form of capacitor or inductor input is:

LM NI N2 VALUE CM NI N2 VALUE

- where L and C signify inductor and capacitor respectively,

- M is the number of the capacitor or inductor,

- N1 and N2 are the nodes which the capacitor or inductor is between,

- and VALUE is the value of the capacitor or inductor in farads or hsnrys.

Typical capacitor and inductor specifications are:

Cl 1 5 .00001 L90 35 0 .5798

Checks are run for unacceptable alpha characters, incorrect number of node numbers entered, node or element numbers which are not integers or are out of bounds, shorted elements, and duplicate elements, where duplicate means two capacitors or two inductors with the same element number.

#### **3.3.** Gyrators

The basic form of gyrator input is: GYRAM NI N2 N3 N4 VALUE

- where GYRA signifies 'gyrator.

- M is the number of the <u>c</u>vrator.

- N1, N2, N3, and N4 are the nodes which the gyrator is connected to,

- and VALUE is the value of the unitless multiplier.

A brief discussion is in order here. NI and N3 correspond to the positive ends of the voltages and N2 and N4 correspond to the negative ends. The equation of the gyrator can be written as:

I \* -(VALUEHV1-V2) 1^ \* (VALUEXV3-V4)

That is, the current on each side of the gyrator is proportional to the voltage on the other side. The proportionality constant is" «7- VALUE.

Typical gyrator specifications are:

GYRA1 10 3 0 5 GYRA43 9 15 34 22 10

Checks are run for for unacceptable alpha characters, element numbers or nodes which are not integers or are out of bounds, incorrect number of nodes specified, shorted gyrators, and duplicate elements, where duplicate means two gyrators with the same element number.

#### 3.4. Linear Current Controlled Current Sources

The basic form of linear current controlled current sources is: CCCSM N1 N2 N3 N4 VALUE

- where CCCS indicates a linear current controlled current source,

- M is the number of the current controlled current source,

- N1, N2, N3, and N4 are the nodes which the CCCS is connected to,

- and VALUE is the value of the unitless multiplier.

Nodes NI and N2 are connected to the controlled source. Nodes N3 and N4 are connected to the controlling current NI and N3 denote  $\ll$  nodes and N2 and N4 denote  $\ll$  nodes. It is important to note that N3 and N4 are actually shorted nodes. That is, no other element may connect nodes 3 and 4 since the simulator internally puts a 0-valued voltage source across these nodes to determine current. The equation of the CCCS may be written:

$$I = (VALUE)!$$

That is, the current on one side of the CCCS is proportional to the current on the other side. The proportionality constant is VALUE.

```

Typical CCCS specifications are:

CCCS1 1 2 3 4 50

CCCS67 23 456 32 123 2

```

Checks are run for unacceptable alpha characters, elemenl numbers or nodes which are not integers or are out of bounds, shorted CCCSs (note that nodes 3 and 4 may not be the same

node number), incorrect number of nodes specified, and duplicate elements, where duplicate means two CCCSs with the same element number.

#### 3.5. Linear Current Controlled Voltage Sources

The basic form of linear current controlled voltage source input is: CCVSM N1 N2 N3 N4 VALUE

- where CCVS signifies current controlled voltage source,

- M is the number of the current controlled voltage source,

- N1, N2, N3, and N4 are the nodes which the CCVS is connected to,

- and VALUE is the value of the multiplier in ohms.

Nodes N1 and N2 are connected to the controlled voltage source. Nodes N3 and N4 are connected to the controlling current. N1 and N3 denote (+) nodes and N2 and N4 denote (-) nodes. Once again, nodes 3 and 4 are shorted because of the internal 0-valued voltage source. The equation of the CCVS may be written:

$(V1 - V2) = (VALUE)I_{3-1}$

That is, the voltage on one side of the CCVS is proportional to the current on the other side. The proportionality constant is VALUE.

Typical CCVS specifications are:

CCVS1 1 2 3 4 10 CCVS34 98 333 52 772 2

Checks are run for unacceptable alpha characters, element numbers or nodes which are not integers or are out of bounds, incorrect number of nodes specified, shorted CCVSs (nodes 3 and 4 may not be the same number), and duplicate elements, where duplicate means two CCVSs with the same element number.

#### 3.6. Linear Voltage Controlled Current Sources

The basic form of linear voltage controlled current sources is: . VCCSM N1 N2 N3 N4 VALUE

- where VCCS signifies voltage controlled current source.

- M is the number of the voltage controlled current source,

- N1, N2, N3, and N4 are the nodes which the VCCS is connected to,

- and VALUE is the value of the multiplier in mhos.

Nodes N1 and N2 are connected to the controlled current source. Nodes N3 and N4 are

connected to the controlling voltage. Nl and N3 denote (+> nodes and N2 and N4 denote (-> nodes. Any element may be placed between nodes 3 and 4. The equation of the VCCS may be written:

I - VALUE(V3 - V4)

That is. the current on one side of the VCCS is proportional to the voltage on the other side. The proportionality constant is VALUE.

Typical VCCS specifications are: VCCS1 2 3 4 5 10

VCCS23 34 56 67 87 2

Checks are run for unacceptable alpha characters, element numbers or nodes which are not integers or are out of bounds, incorrect number of nodes specified, shorted VCCSs and duplicate elements, where duplicate means two VCCSs with the same element number.

#### 3.7. Linear Voltage Controlled Voltage Sources

The basic form of linear voltage controlled voltage source input is: VCVSM N1 N2 N3 N4 VALUE

- where VCVS signifies voltage controlled voltage source.

- M is the number of the voltage controlled voltage source,

- N1, N2, N3, and N4 are the nodes which the VCVS is connected to,

- and VALUE is the value of the unitless multiplier.

Nodes N1 and N2 are connected to the controlled voltage source. Nodes N3 and N4 are connected to the controlling voltage. N1 and N3 denote (+) nodes and N2 and N4 denote (-> nodes. Any element may be placed between nodes 3 and 4. The equation of a VCVS may be written as:

(VI - V2) = VALUE(V3 - V4)

That is, the voltage on one side of the VCVS is proportional to the voltage on the other side. The proportionality constant is VALUE.

Typical VCVS specifications are:

VCVS1 1 2 3 4 10 VCVS34 45 65 789 12 2

í

Checks are run for unacceptable alpha characters, element numbers or nodes which are not integers or are out of bounds, incorrect number of nodes specified, shorted VCVSs, and duplicate elements, where duplicate means two VCVSs with the same element number.

#### 3.8. Constant Voltage Sources

i

ş

The basic form of constant voltage source input is: VM.N1 N2 VALUE

- where V signifies constant voltage source,

- M is the number of the voltage source.

- N1 and N2 are the nodes which the voltage source is between,

- and VALUE is the value of the voltage source in volts.

NI is the positive node of the voltage source and N2 is the negative node. The voltage source current is defined as flowing from node 1 to node 2. Typical voltage source specifications are:

VI 1 0 5 . V23 456 34 15

Checks are run for unacceptable alpha characters, node or element numbers which are not integers or are out of bounds, shorted elements, incorrect number of nodes entered, duplicate constant voltage sources and duplicate transient voltage sources, where duplicate means two voltage sources with the same element number.

#### 3.9. Constant Current Sources

The basic form of constant current source input is: IM N1 N2 VALUE

- where I signifies constant current source.

- M is the number of the current source,

- NI and N2 are the nodes which the current source is between,

- and VALUE is the value of the current source in amps.

The current from the current source is defined as flowing from node 1 to node 2 through the current source. Typical current source specifications are:

II 1 2 5

134 27 0 10

Checks are run for unacceptable alpha characters, node or element numbers which are not integers or are out of bounds, incorrect number of nodes entered, shorted elements, duplicate constant current sources and duplicate transient current sources, where duplicate means two current sources . with the sama element number.

#### 3.10. Transient Voltage Sources

The basic form of transient voltage source input is: TRANVM NI N2 TYPE PARAMETERS

- where TRANV signifies transient voltage source,

- M is the number of the transient voltage source,

- NI and N2 are the nodes which the transient source is between.

- TYPE indicates the type of transient source, (one of PWL &. SIN)

- and PARAMETERS are parameters required by the specific type.

NI is the positive node of the voltage source and N2 is the negative node. Current flows through the transient source identically to the constant source. For TYPE specifications, see section 3.11.1 on allowable type information.

Typical transient voltage source specifications are:

#### TRANVI 1 0 PWL 0 C 1 10 2 10 3 20 TRANV34 45 93 SIN 0 1 I 0 0

Checks are run for unacceptable alpha characters, element numbers or nodes which are net integers or are out of bounds, incorrect number of nodes specified, shorted transient sources, incorrect numbers of parameters specified, incorrect types specified, duplicate transient voltage sources and duplicate constant voltage sources, where duplicate means two voltage sources with the same element number.

#### 3.11. Transient Current Sources

The basic form of transient current source input is: TRANIM N1 N2 TYPE PARAMETERS

- where TRANI signifies transient current source,

- M is the number of the transient voltage source,

- NI and N2 are the nodes which the transient source is between,

- TYPE indicates the type of transient source (one of PWL 4: SIN),

- and PARAMETERS are parameters required by the specific type.

For TYPE specifications, see the following section on allowable types. NI is the positive node of the current source and N2 is the negative node.

Typical transient current source specifications are:

#### TRANI1 1 0 PWL 0 0 1 10 2 10 3 20 TRANI34 45 93 SIN 0 1 1 0 0

Checks are run for unacceptable alpha characters, element numbers or nodes which are not integers or are out of bounds, incorrect number of nodes specified, shorted transient sources, incorrect numbers of parameters specified, incorrect types specified, duplicate transient current sources and duplicate constant current sources, where duplicate means two current sources with the same element number.

#### 3.11.1. Allowable Types