# NOTICE WARNING CONCERNING COPYRIGHT RESTRICTIONS:

The copyright law of the United States (title 17, U.S. Code) governs the making of photocopies or other reproductions of copyrighted material. Any copying of this document without permission of its author may be prohibited by law.

# RAPIDbus: Design of an Extensible Multiprocessor Structure

John C. Willis Arthur C. Sanderson

CMU-RI-TR-84-13

Department of Electrical and Computer Engineering

The Robotics Institute

Carnegie-Mellon University

Pittsburgh, Pennsylvania 15213

May 1984

Copyright © 1984 Carnegie-Mellon University

This work was supported in part by The National Science Foundation under grant number 7923893. Portions of the work described here, particularly the RAPIDbus II design, were supported by the Air Force Office of Scientific Research under contract number F49620-83-C-0100.

# Table of Contents

| 1. Why RAPIDbus?                                                | 3        |

|-----------------------------------------------------------------|----------|

| 1.1. Defining the Application                                   | 4        |

| 1.1.1. Model of a Robotic System                                | 4        |

| 1.1.1.1. Internalization                                        | 4        |

| 1.1.1.2. Knowledge Base Management                              | 6        |

| 1.1.1.3. Goal Management                                        | 6        |

| 1.1.1.4. Extemalization                                         | 6        |

| 1.1.2. Machine Vision                                           | 7        |

| 1.1.3. Assembly Assistance                                      | 8        |

| 1.1.4. Design Assistance                                        | 8        |

| 1.2. RAPIDbus                                                   | 10       |

| 1.2.1. Defining a Structure                                     | 10       |

| 1.2.2. The Goal                                                 | 10       |

| 2. RAPIDbus I: Architecture and Realization                     | 11       |

| 2.1. Why Build?                                                 | 11       |

| 2.2. Systems Architecture                                       | 12       |

| 2.2.1. Choosing Versabus as a Host                              | 12       |

| 2.2.2. PMS Level Alternatives                                   | 14       |

| 2.2.3. The RAPIDbus I Interface                                 | 16       |

| 2.2.3.1. RAPIDbus I Concept                                     | 16       |

| 2.2.3.2. RAPIDbus functional modules                            | 18       |

| 2.3. Communications Protocol                                    | 21       |

| 2.3.1. The 68000                                                | 21       |

| 2.3.1.1. Memory Reference Cycles                                | 22       |

| 2.3.1.2. Interrupt Cycles                                       | 23       |

| 2.3.2. The Versabus Data Transfer                               | 23       |

| 2.3.2.1. Bus Arbitration                                        | 24       |

| 2.3.2.2. Data Transfer                                          | 24       |

| 2.3.2.3. Interrupt Handling 2.3.3. The RAPIDbus I Data Transfer | 25<br>25 |

| 2.3.3.1. Data Transfer                                          | 25<br>25 |

|                                                                 | 25<br>26 |

| 2.3.3.2. Interrupt Handling 2.3.3.3. Multicasting               | . 26     |

| 2.3.3.5. Multicasting 2.4. Evaluation Net Modeling              | 27       |

| 2.4.1. Use of Evaluation Nets for Hardware Modeling             | 27<br>27 |

| 2.4.2. Caveats                                                  | 30       |

| 2.4.3. The VM02 Dual Port Processor                             | 30       |

| 2.4.4. System Memory Cards                                      | 34       |

| 2.4.5. The Versabus Interconnect                                | 34       |

| 2. No. 1110 Volododo intologimiot                               | 04       |

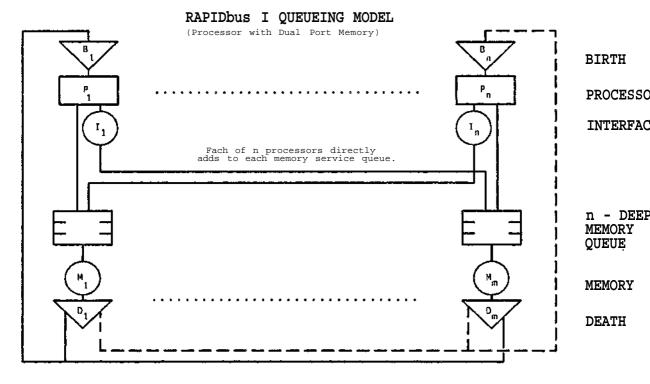

| 2.4.6. The RAPIDbus Interconnect                      | 35 |

|-------------------------------------------------------|----|

| 3. RAPIDbus I: An Evaluation                          | 37 |

| 3.1. Evaluation Methodology                           | 37 |

| 3.2. Architecture                                     | 39 |

| 3.2.1. Supporting Broad Task Concurrency              | 39 |

| 3.2.2. Host Homogeneity                               | 41 |

| 3.2.3. Reliability                                    | 42 |

| 3.2.4. Programmability                                | 42 |

| 3.2.5. Societies of Processors                        | 44 |

| 3.3. Implementation                                   | 44 |

| 3.3.1. System Structure                               | 44 |

| 3.3.1.1. Simulation Methodology                       | 44 |

| 3.3.1.2. Versabus - Separate Processors and Memory    | 45 |

| 3.3.1.3. RAPIDbus I - Bus Memory                      | 47 |

| 3.3.1.4. Versabus - Local and Global Processor Memory | 47 |

| 3.3.1.5. RAPIDbus I - Local and Bus Memory            | 51 |

| 3.3.1.6. Versabus - Dual Ported Memory                | 51 |

| 3.3.1.7. RAPIDbus I - Dual ported Memory              | 53 |

| 3.3.1.8. Structural Conclusions                       | 55 |

| 3.3.2. Bus Utilization                                | 58 |

| 3.3.3. Bus Allocation                                 | 60 |

| 3.3.4. Interrupt Structure                            | 61 |

| 3.3.5. Multicast Capability                           | 62 |

| 3.4. Realization                                      | 63 |

| 3.4.1. Asynchrony                                     | 63 |

| 3.4.2. System Complexity                              | 68 |

| 3.4.3. Bus Interface Integration                      | 71 |

| 3.4.4. Fabrication Technology                         | 73 |

| 3.4.4.1. Power Supply Engineering                     | 73 |

| 3.4.4.2. Interconnect Engineering                     | 75 |

| 3.4.4.3. Thermal Engineering                          | 75 |

| 3.5. Major Contributions                              | 77 |

| 4. RAPIDbus II: Architecture                          | 79 |

| 4.1. The Goal                                         | 79 |

| 4.2. Architectural Specification                      | 79 |

| 4.3. Extensibility                                    | 80 |

| 4.3.1. Heterogeny of Elements                         | 81 |

| 4.3.2. Software Support                               | 83 |

| 4.3.3. Modularity                                     | 85 |

| 4.3.4. Specification Summary                          | 87 |

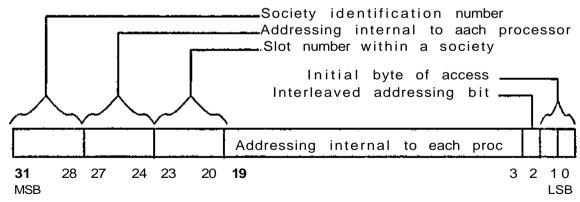

| 4.4. Addressing                                       | 87 |

| 4.4.1. Memory Map Structure                           | 88 |

| 4.5. Data Formats                                     | 89 |

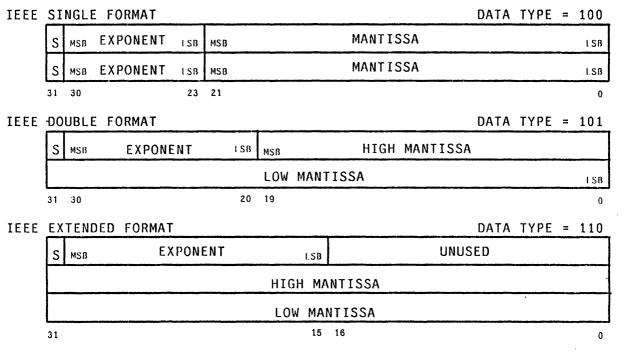

| 4.5.1. Scalar Data Types                              | 90 |

| 4.5.2. Floating Point Data Types                      | 92 |

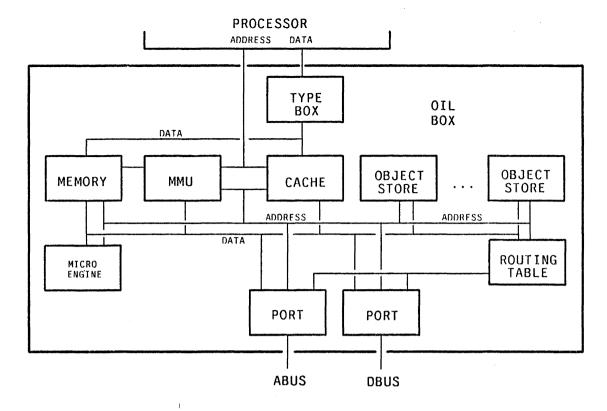

| 4.6. Upward Compatibility: OIL                        | 92 |

| 4.6.1. Objects                                        | 92 |

| 4.6.2. Object Support                                 | 93 |

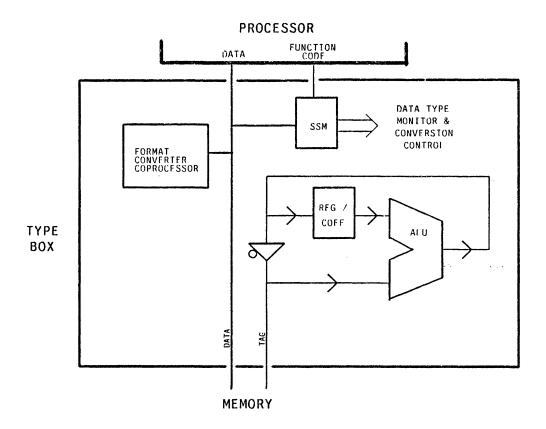

| 4.6.3. Data Typing                                    | 95 |

|                                                       |    |

|                                                                        | iii        |

|------------------------------------------------------------------------|------------|

| 4.6.4. Garbage Collection                                              | 96         |

| 4.6.5. Summary                                                         | 97         |

| 5. RAPIDbus II: Implementation & Realization                           | 99         |

| 5.1. The Implementation                                                | 99         |

| 5.1.1. Packet Switching Structure                                      | 100        |

| 5.1.1.1. Packet Routing                                                | 103        |

| 5.1.1.2. Bus Justification                                             | 106        |

| 5.1.1.3. Bus Allocation                                                | 107        |

| 5.1.2. Data Transfer                                                   | 107        |

| 5.1.2.1. Single Cycle Read Request                                     | 108        |

| 5.1.2.2. Single Cycle Write Request                                    | 110        |

| 5.1.2.3. Multiple Cycle Read Request                                   | 110        |

| 5.1.2.4. Multiple Cycle Write Request                                  | 111        |

| 5.1.2.5. Read-Modify-Write Request                                     | 112        |

| 5.1.2.6. Single Cycle Read Service 5.1.2.7. Single Cycle Write Service | 112<br>113 |

| 5.1.2.8. Multiple Cycle Read Service                                   | 114        |

| 5.1.2.9. Multiple Cycle Write Service                                  | 114        |

| 5.1.2.10. Read-Modify-Write Service                                    | 115        |

| 5.1.2.11. Repeater Forward Service                                     | 115        |

| 5.1.2.12. Repeater Forward Request                                     | 116        |

| 5.1.2.13. Interrupt Generation                                         | 116        |

| 5.1.2.14. Interrupt Reception                                          | 117        |

| 5.1.3. System Reliability                                              | 117        |

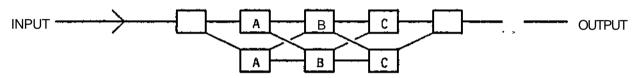

| 5.1.3.1. Interchange Redundancy                                        | 117        |

| 5.1.3.2. Diagnostic Assistance                                         | 118        |

| 5.1.4. Upward Compatibility                                            | 119        |

| 5.1.4.1. Parallel Switching Plane                                      | 120        |

| 5.2. Realization                                                       | 124        |

| 5.2.1. Physical Structure                                              | 124        |

| 5.2.2. Microcoded Host Interface                                       | 124        |

| 5.2.3. Timing Analysis 5.2.3.1. Local Memory Access                    | 129<br>129 |

| 5.2.3.2. RAPIDbus Access                                               | 129        |

| 5.2.4. Evaluation Methodology                                          | 130        |

| 5.2.5. Extended Versabus Simulation                                    | 131        |

| 5.2.6. RAPIDbus Society Simulation                                     | 132        |

| 5.2.7. The Design Space                                                | 134        |

| 5.2.7.1. RAPIDbus I                                                    | 134        |

| 5.2.7.2. RAPIDbus II                                                   | 134        |

| 5.2.7.3. VAX - SBI                                                     | 134        |

| 5.2.7.4. University College, London                                    | 135        |

| 5.2.7.5. CA2 - Hamburg                                                 | 136        |

| 5.2.7.6. Synapse N + 1                                                 | 136        |

| 5.2.7.7. APTEC DPS                                                     | 137        |

137

137

5.2.7.8. C.MMP

5.2.7.9. CM\*

| 6. Conclusions      | 13 |

|---------------------|----|

| 6.1. Architecture   | 13 |

| 6.2. Implementation | 14 |

| 6.3. Realization    | 14 |

| 6.4. Trial by Fire  | 14 |

46

# List of Figures

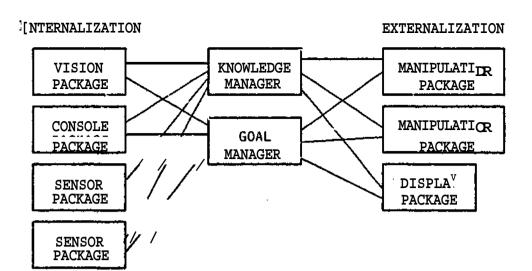

| Figure 1-1:   | Computational resources supporting many robotics applications can be summarized as a system with internalization, knowledge | 5   |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

|               | management, goal management, and externalization packages.                                                                  |     |

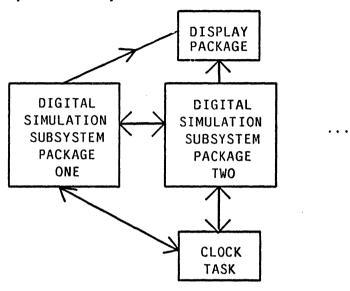

| Figure 1-2:   |                                                                                                                             | 9   |

| riguio i z.   | process communication along well defined interface paths can                                                                | •   |

|               | improve simulator throughput.                                                                                               |     |

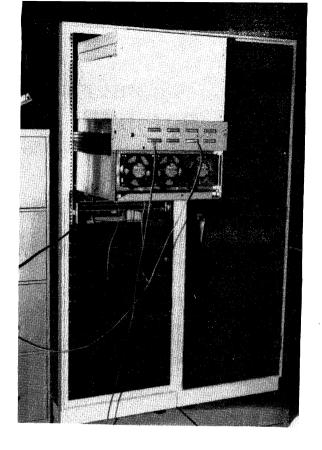

| Figure 2-1:   | A dual height Versabus card cage was constructed to house the two                                                           | 12  |

| rigule 2-1.   | processor RAPIDbus I prototype.                                                                                             | 12  |

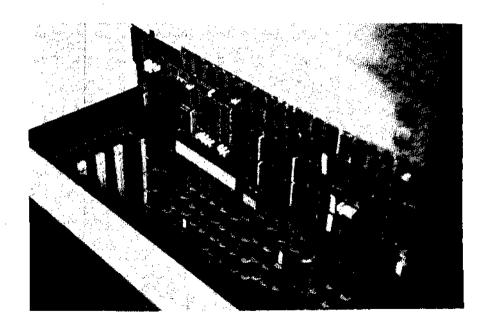

| Figure 2.2.   | The RAPIDbus I interface was implemented on a mother-daughter                                                               | 13  |

| riguio z · z. | board inserted between the physical bus and a commercial                                                                    |     |

|               | monoboard computer.                                                                                                         |     |

| Figure 2-3:   | Separation of processor and memory functions on the bus maximizes                                                           | 14  |

|               | bus loading and average memory reference latency.                                                                           | • • |

| Figure 2-4:   | Addition of local memory on the processor card permits quick access                                                         | 15  |

| J             | to private data and instructions.                                                                                           |     |

| Figure 2-5:   | Dual porting of the local memory can economize on bus cycles                                                                | 16  |

|               | required to access shared memory.                                                                                           |     |

| Figure 2-6:   | The virtual bus system is implemented using bus windows to link                                                             | 17  |

|               | several masters and slaves simultaneously.                                                                                  |     |

| Figure 2-7:   | Each RAPIDbus interface card is composed of multiple modules,                                                               | 18  |

|               | centered around the lbus.                                                                                                   |     |

| Figure 2-8:   | Bus transfer timing relative to the processor clock for two cycles, the                                                     | 22  |

|               | first in zero wait states, the second requiring an extra clock cycle.                                                       |     |

| Figure 2-9:   | Locations and transitions are used to represent control flow using                                                          | 28  |

|               | evaluation net notation.                                                                                                    |     |

| Figure 2-10   | : The processor's local bus allows access to local memory, board                                                            | 31  |

|               | registers, and the Versabus port.                                                                                           |     |

| Figure 2-11   | : The local ram is dual ported to both the Versabus and the local                                                           | 32  |

|               | processor bus.                                                                                                              |     |

| Figure 2-12   | : The dual port arbiter allows a connection between local bus and                                                           | 33  |

|               | Versabus or between local ran and the Versabus.                                                                             |     |

| Figure 2-13   | : System memory cards resemble VM02 ram cards without the dual-                                                             | 34  |

|               | port arbitration.                                                                                                           |     |

| Figure 2-14   | : The Versabus interconnect protocol assigns the single physical bus                                                        | 35  |

|               | to a particular bus for the duration of of a data transfer operation.                                                       |     |

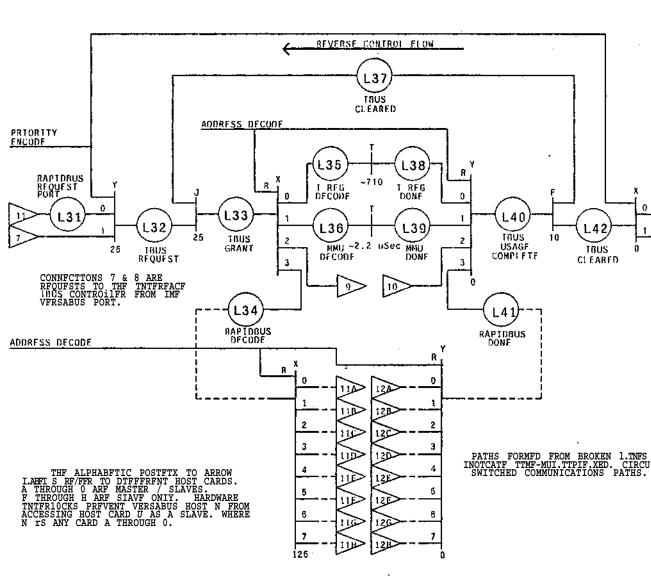

| Figure 2-15   | : The RAPIDbus interconnect provides four virtual bus paths, each of                                                        | 35  |

|               | which is described by the graph above.                                                                                      |     |

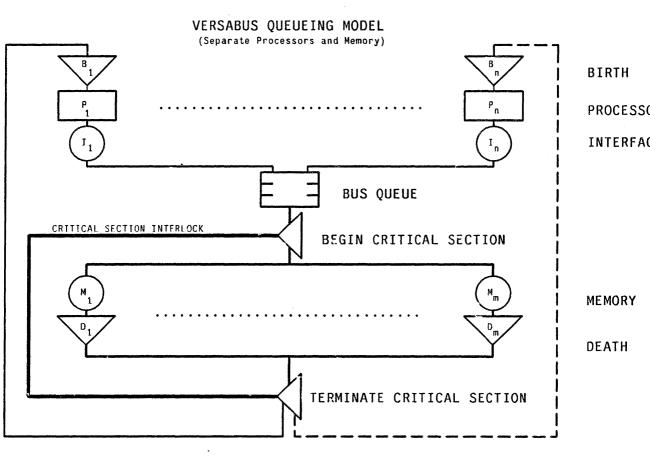

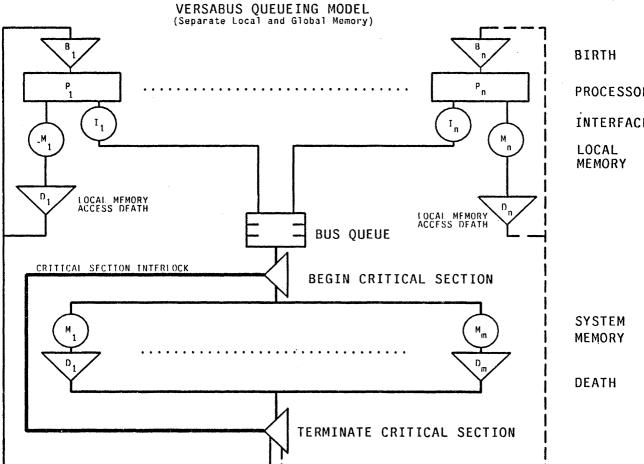

Figure 3-1: Use of separate processor and memory cards forces all processors to

be served by a central memory server on all memory reference cycles.

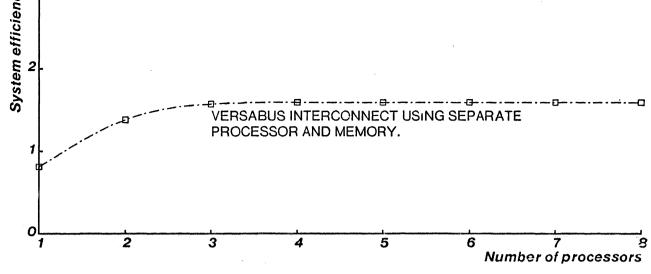

| on the bus, our system would level out at less than twice the                                                                                                                                              | 47 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

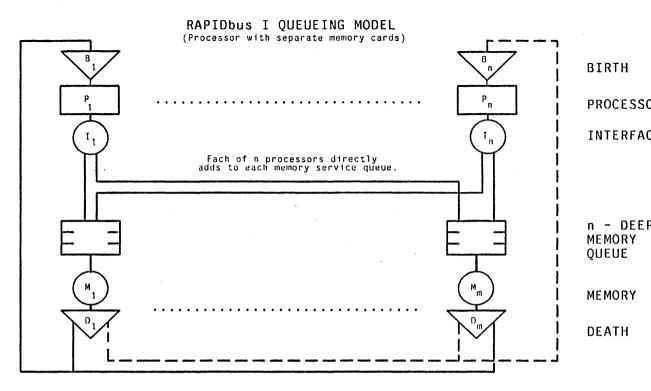

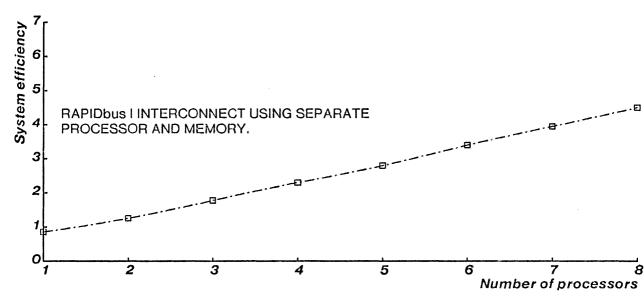

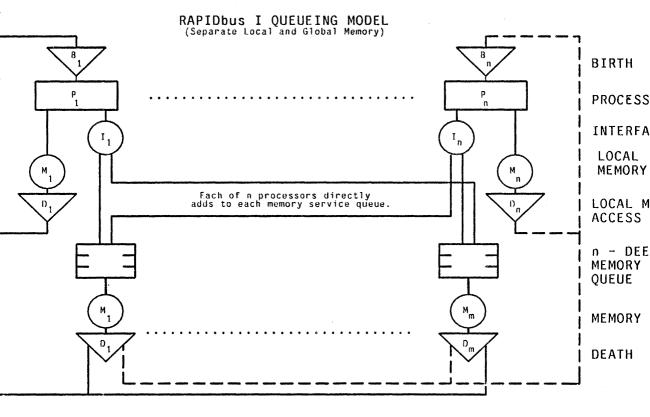

| performance of a single processor.  Figure 3-3: Addition of the RAPIDbus interface to a Versabus system with separate processors and memory removes the critical section enveloping bus memory.            | 48 |

| Figure 3-4: Separate processors and memory cards running with the RAPIDbus interface dramatically improve the throughput, but in an absolute sense, still runs poorly.                                     | 48 |

| Figure 3-5: Addition of local memory on each processor decreases contention for main memory while increasing the complexity of memory allocation.                                                          | 49 |

| Figure 3-6: Addition of local memory decreases load on the system bus at the expense of a possible increase in the complexity of the programming environment.                                              | 50 |

| Figure 3-7: Addition of RAPIDbus interfaces to a Versabus system with local memory removes bus contention for those references mapped to the system bus.                                                   | 52 |

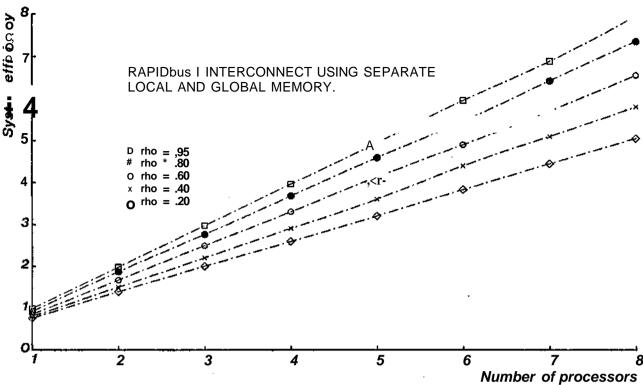

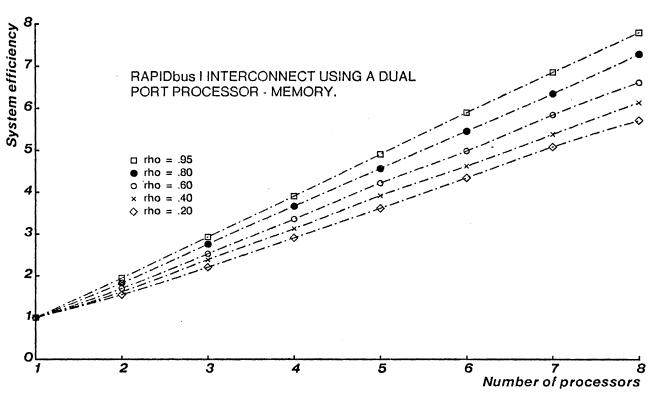

| Figure 3-8: Addition of RAPIDbus interface cards decreases contention for the system bus, improving performance in systems with low $\rho$ and more than three processors.                                 | 53 |

| Figure 3-9: Dual porting the local memory to the system bus decreases bus contention relative to separate memory cards without the disadvantages of purely local memory.                                   | 54 |

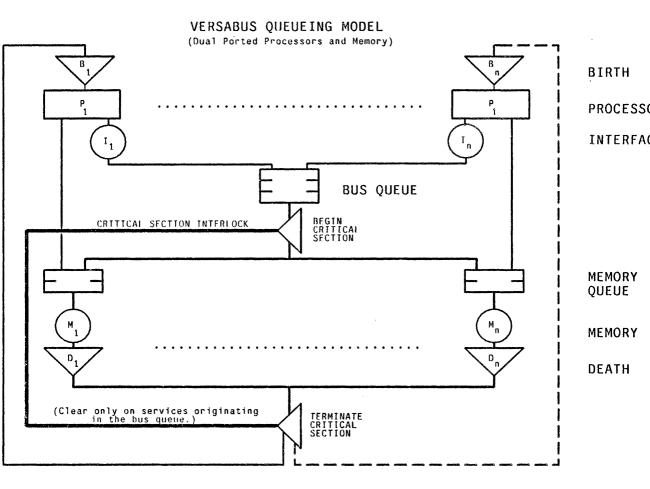

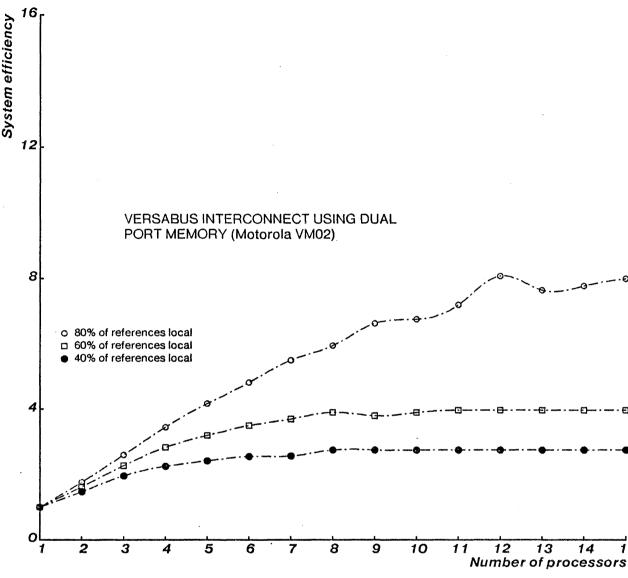

| Figure 3-10: Dual porting the memory local to the processor decreases bus contention and simplifies restarting a suspended process.                                                                        | 55 |

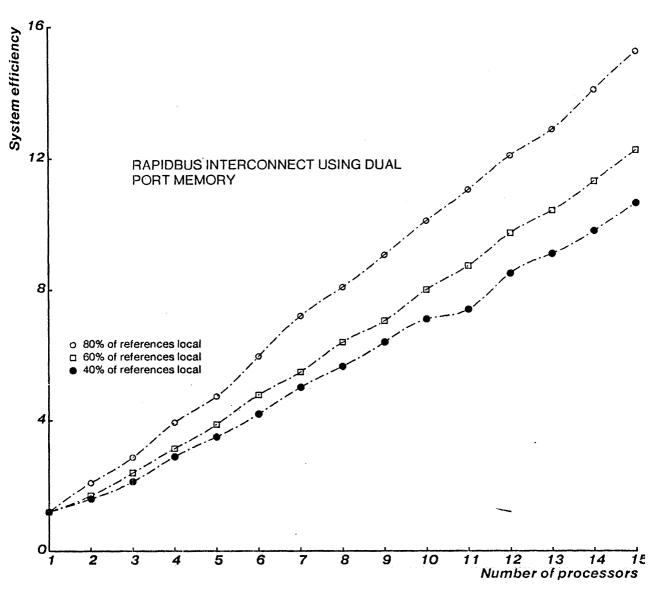

| Figure 3-11: Addition of a RAPIDbus interface to a dual port Versabus system decreases bus contention while introducing the possibility of deadlock.                                                       | 56 |

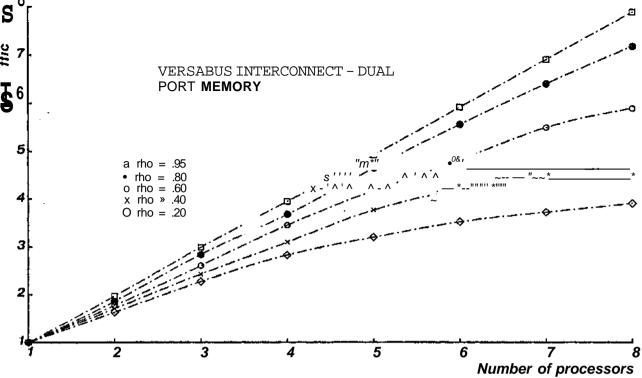

| Figure 3-12: Addition of the RAPIDbus interface to a dual port system produces a very limited increase in system throughput for any but the lowest $\rho$ values.                                          | 57 |

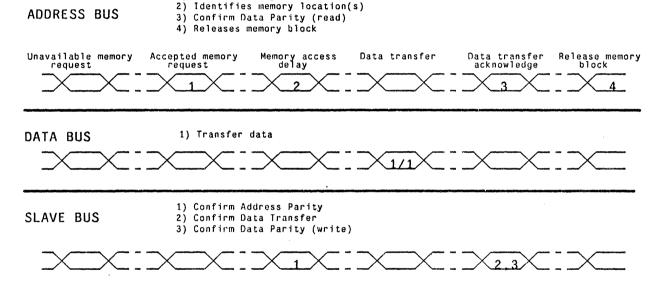

| Figure 3-13: Analysis of the information content during each window of a RAPIDbus I data transfer operation suggests more efficient transmission protocols.                                                | 58 |

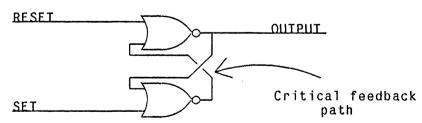

| Figure 3-14: Bistable elements, designed conceptually like that above form the basis of the metastable problem.                                                                                            | 63 |

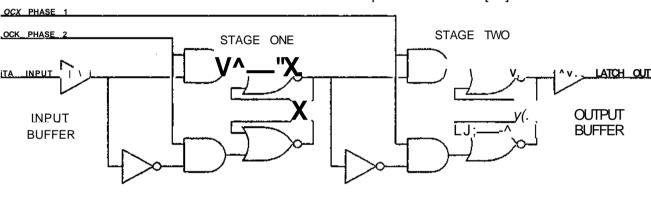

| Figure 3-15: A D latch, key to the design of synchronizers, can be represented by structures the two stage structure shown above.                                                                          | 64 |

| Figure 3-16: The metastable voltage is surrounded by a small probabilistic region, where escape is noise dependent, and a larger deterministic region where the propagation delay is design dependent.     | 65 |

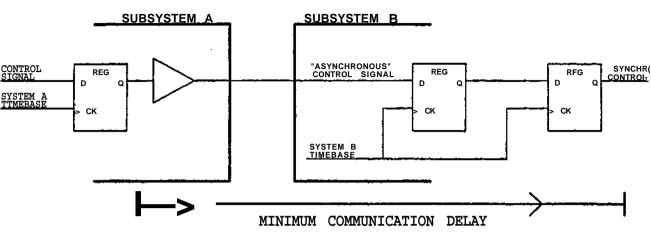

| Figure 3-17: Design of a practical system using an asynchronous interface requires a synchronization latency to increase the mean time between metastables that propagate through to the second subsystem. | 66 |

| Figure 3-18: Package distribution on RAPIDbus I interface cards.                                                                                                                                           | 70 |

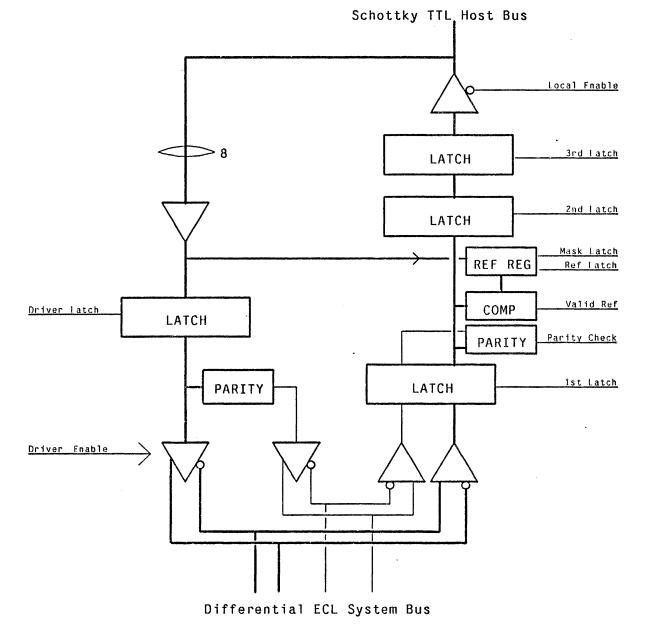

| Figure 3-19: Consolidation of latches, drivers, parity logic, and comparators into a translator slice results in a fast, compact time-multiplexed bus.                                                     | 72 |

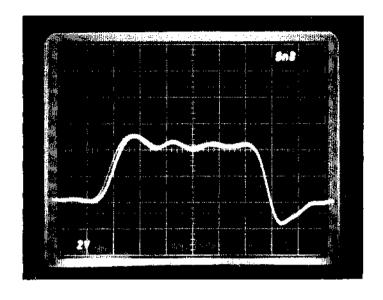

| Figure 3-20: Use of a good ground place, bypassing, and short lines, acceptable waveforms were achieved using wire wrap on RAPIDbus I.                                                                     | 76 |

| Figure 3-21  | : RAPIDbus I system specifications.                                                                                                                                                                      | 77         |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

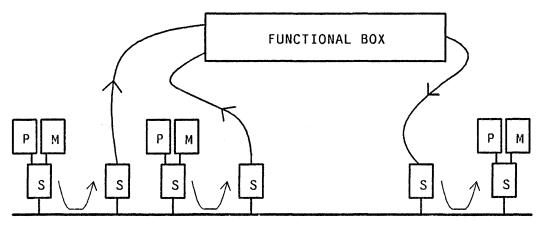

| Figu re 4-1: | Multiword packets can be used to integrate a prototype functional box onto RAPIDbus while existing processors absorb overhead                                                                            | 82         |

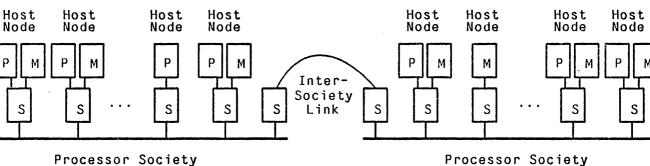

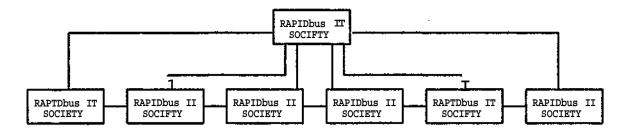

| Figure 4-2:  | functionality.  The RAPIDbus II architecture is composed of societies with up to fifteen host nodes. High speed parallel links between societies can be configured in response to research requirements. | 85         |

| Figure 4-3:  | A pipeline of societies fits applications where most of the data flow obeys a linear, single input port, single output port relationship.                                                                | 86         |

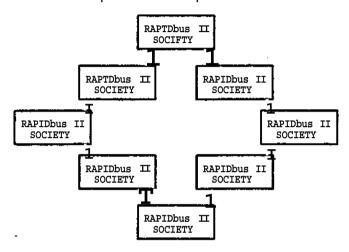

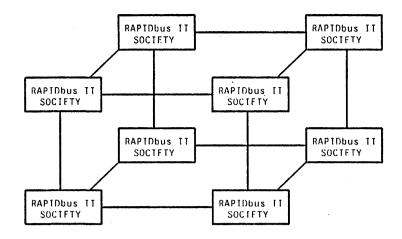

| Figure 4-4:  |                                                                                                                                                                                                          | 86         |

| Figure 4-5:  | Rings of societies can be generalized into N-cube topologies, with arbitrarily many redundant paths between societies at the price of increased overhead.                                                | 87         |

| Figure 4-6:  | The physical address space is partitioned hierarchically into societies and then host nodes within a society.                                                                                            | 88         |

| Figure 4-7:  | Five primative scalar data types are supported based on Motorola 68000 representations.                                                                                                                  | 90         |

| Figure 4-8:  | Three different floating point representations are supported based on<br>the Motorola packing of the proposed IEEE floating point<br>specification P754.                                                 | 91         |

| Figure 4-9:  | The object interface layer is inserted between processor and interchange to assist in operand management.                                                                                                | 94         |

| Figu re 4-10 | : The type box is used to retrofit a variety of existing processors to an object based RAPIDbus II.                                                                                                      | 96         |

| Figure 5-1:  | The least significant three bits of the function code field indicate the transfer class.                                                                                                                 | 102        |

| Figure 5-2:  | The most significant five bits of the function code elaborate on the class of the transfer.                                                                                                              | 103        |

| Figure 5-3:  | Each primary bus has a paired acknowledge bus to confirm each bus cycle.                                                                                                                                 | 104        |

| Figure 5-4:  | Timing for the high speed buses is done by one arbiter module global                                                                                                                                     | 104        |

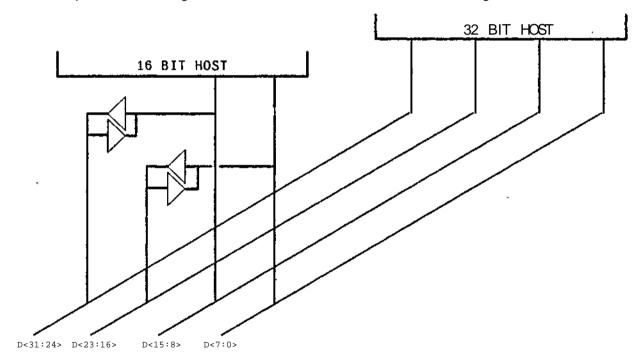

| Figure 5-5:  | to each cage.  Use of a sixteen bit host on a thirty-two bit unjustified bus requires a                                                                                                                  | 106        |

| Figure 5-6:  | ·                                                                                                                                                                                                        | 118        |

| Figure 5-7:  | sources of failure, any one of which can fail the system.  Dividing a system into many, spared modules can increase fault                                                                                | 118        |

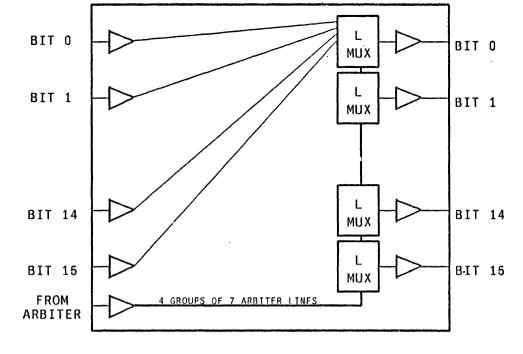

| Figure 5-8:  | tolerance.  Bit slice crosspoint switch permits changing one routing per cycle in                                                                                                                        | 121        |

| Figure 5-9:  | each of four groups.  Many of the same fields carried in parallel with the common bus implementation are doublet serialized with the crosspoint switch, decreasing data path width.                      | 122        |

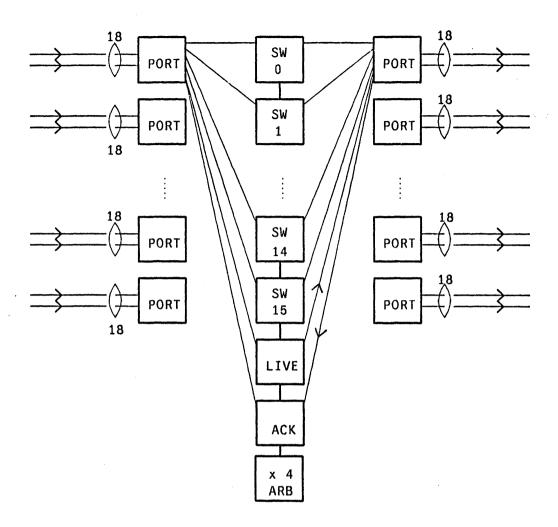

| Figure 5-10: | Eighteen bit slice crosspoint chips interconnect a society of RAPIDbus II processor nodes.                                                                                                               | 123        |

| •            | <ul> <li>RAPIDbus II proof-of-concept realization.</li> <li>A micro-coded RAPIDbus interface simplifies the integration of existing processor nodes.</li> </ul>                                          | 125<br>126 |

- Figure 5-13: Versabus systems quickly saturate in a tightly coupled system such that increasing the number of processors does not improve the throughput.

- Figure 5-14: Use of a RAPIDbus II interchange network significantly reduces bus contention in a tightly coupled application with respect to a similar Versabus system.

# **Abstract**

Research in areas of robotics such as machine vision and control systems can benefit from appropriate increases in the available computational power. If algorithms can be structured to take advantage of task level concurrency, a multiprocessor design can provide cost-effective enhancements to the computational resources while decreasing the impact of subsystem failures.

RAPIDbus is described in this report as two evolutionary steps in the development of a system to support research in advanced, integrated, sensor based robotic systems. RAPIDbus I, a four processor architecture, is evaluated based on a two processor implementation fabricated in the laboratory. Building on the first design, RAPIDbus II is described as an extensible, high performance, packet switched structure supporting a multitude of heterogeneous processor-memory nodes.

Both RAPIDbus architectures assume a single address space populated by a moderate number of comparatively powerful processors. RAPIDbus II goes beyond the breadtn of the earlier architecture by assembling groups of fifteen processors into ensembles called societies. Packet repeaters between societies allow up to sixteen ensembles to be assembled in a problem-dependent configuration within a single shared address space. Although not realized in the current proof-of-concept system, an object layer interface was suggested to maintain cache coherency, support strong data typing, and assist in dynamic memory management.

The RAPIDbus II implementation independently allocates bandwidth in each society using redundant, time-multiplexed busses and an efficient bus transfer mechanism. Both single and multiple word transfers are supported to match the needs of different tasks and processors. An upward compatible implementation is suggested which replaces the busses in each society with a cross-point switch, increasing performance while decreasing complexity.

Realization of prototype hardware led to exploration of asynchronous interface design, system complexity, and integration level issues. Embodiment of the architecture and implementation in hardware allows comparison with other designs, helping to locate RAPIDbus within the multiprocessor design space.

# Acknowledgements

This project report reflects the assistance of many people who, while not necessarily endorsing the structure, have helped to bring the structure to life. RAPIDbus I is derived in part from design concepts developed by Mario Zoccoli and Rafael Bracho.

Dave Coleman, Rob Emmons, and Paul Oppedal are providing essential assistance to transform drawings into working hardware. Under IBM sponsorship, Pat Snyder of the University of Minnesota Micro group is bringing parts and supplier relations together in record time. Design automation was made possible by Dario Giuse's prompt and patient support of early versions of drawing package. Thanks are also due to Howard Wactlar and the engineering lab for providing the kind of support that makes *almost* anything possible.

Complementary to the hardware structure, Nanda Alapati and Jim McQuade are bringing a software environment together with the assistance of Industrial Programming Inc.

RAPIDbus I was supported by the National Science Foundation. Architectural design and partial fabrication of RAPIDbus II is being supported by the Air Force Office of Scientific Research as a tool in the exploration of space based image analysis algorithms. Colin Harrison and Dale Krutchten with IBM's Instrument's Advanced Technology Division are supporting fabrication of the RAPIDbus I! implementation. SKY Computer is providing essential hardware and support for the floating point processor nodes. H. T. Kung supported importation of LLL's SCALD into our environment, and design of the ECL bus interface chip in conjunction with A. Nowatzyk.

The advice and helpful suggestions made by many researchers, designers, and architects at IBM Instruments, Motorola MicroSystems, Motorola Semiconductors, and ESL/TRW are gratefully acknowledged.

# Chapter 1 Why RAPIDbus?

Two hundred kilometers above the earth's surface, a space platform is responsible for the analysis of imagery representing events below. Within a factory of the future, individualized electronic packages are assembled by a team of interacting robots. In the laboratory, a new computer system is taken from design drawings to gate level emulation with minimal human intervention. Hypothetical settings such as these represent goals motivating current robotics research. Each such application is rooted in specific theoretical and implementation questions. They share a common need for appropriate and significant increases in the computational power available to support future development.

RAPIDbus is directed at exploring one approach to providing computational resources for the development of advanced robotic systems. It is both a project in application-directed computer engineering, and a potential research tool. Conceived with such dual purpose, it is a blend of the freedom provided by theoretical computer architecture, and the realities best embodied by the label: tool. By providing a research multiprocessor which is attractive and practical for a select user base, valuable feedback can be generated, improving our understanding of both the application environment, and practical approaches to concurrent programming.

This document describes RAPIDbus as an evolutionary foundation upon which an application dependent configuration and software base can be built. Although both the

software environment and the implementation of the application are critical to a system success, this document explicitly discusses neither beyond motivating the chosen machine architecture.

# 1.1. Defining the Application

RAPIDbus is intended to provide a system architecture which transcends a particular robotics environment, and yet no attempt has been made to create a "general" computing resource. Many special purpose processors have been designed to effectively support a narrow subsystem need. As a multiprocessor, RAPIDbus is intended to combine the efficiency of such processors with the requisite general purpose processor element. Like a visit to a fine tailor, there is no "size" (specific environment) cut into the design, yet a narrow "style" (robotics research) is defined.

# 1.i.1. Model of a Robotic System

From the standpoint of the computer architect, it is useful to create a model for the computational engine within a robot system. Each environment will place slightly different requirements on each subsystem, yet there is an underlying similarity in the structure of each. Figure 1-1 illustrates a variety of internalization tasks interacting with a knowledge base to form an integrated representation of the external environment. A dynamic goal manager relies on the model generated by the knowledge base to provide control directives for packages that modify the external environment.

# 1.1.1.1. Internalization

The internalization stage is one of the most difficult parts of the system, both conceptually and computationally, since the external world is often weakly constrained. In a robust system, this stage may be composed of a multitude of different packages which rely on both sensor devices and the knowledge base for a bottom-up, top-down analysis of the external world. Two-way interaction with a knowledge base functionally separates different internalization media, and while allowing access to a time history of the internal model of the outside world.

Machine vision represents an appealing internalization medium in many applications, both because of the available bandwidth, and by analogy to human strategy. Yet the bandwidth, and the confounding of useful information by a multitude of factors often makes vision the most computationally challenging of the internalization media. Vision represents a primary

Figure 1 - 1: Computational resources supporting many robotics applications can be summarized as a system with internalization, knowledge management, goal management, and externalization packages.

application area guiding the RAPIDbus design.1

Auditory input can be represented as a linear input stream sampled in time, often with much lower bandwidth than three dimensional visual signals.<sup>2</sup> Once sampled, audio processing often is computationally intensive with some of the same qualitative processing requirements as vision [58].

Other internalization media include contact [18], proximity, position, or force sensing. Internalization tasks must convert the sensor input to a representation useful for the knowledge manager.

In contrast to more general computing systems, a user console is very much an ancillary input task. In the laboratory, a console is useful for interacting with the system under development using highly constrained, relatively low bandwidth paths. Seldom is there a

<sup>1</sup> See the subsection following.

Two spatial dimensions and one of time.

need for multiple consoles beyond hardware diagnosis. It is conceivable that a fielded system in the future might have no console at all.

# 1.1.1.2. Knowledge Base Management

Current research directed at a single portion of a robot system of en embodies the knowledge base manager within the internalization and externalization packages. As multiple internalization and externalization packages are added, the concept of a central information repository becomes more important. Packages represent the talents of many different researchers who require a common means of communicating. For instance, tactile, auditory, or other cues might be useful in the selection of relevant visual or other media, yet exposure of one internalization package to another's data structures increases both the conceptual and implementation difficulties. The structure of both such a knowledge base, and the means by which it interacts with internalization packages is an open research topic.

# 1.1.1.3. Goal Management

The goal manager package motivates both the internalization and externalization stages based on the internal state representation maintained by the knowledge manager. For instance, Weiss's visual based servo control might be conceived of as a goal manager which asks the knowledge base to maintain a stream of X and Y coordinates of specific features relative to a reference frame [60]. The goal manager might then instruct the externalization packages globally so as to narrow an arm down on an object of interest. At a higher level, the goal manager might plan the assembly of an object based on a description maintained by the knowledge manager.<sup>3</sup>

# 1.1.1.4. Externalization

The externalization packages attempt to affect the external environment in accordance with the directives of the goal manager package. Generally each package can be expected to merge the internal model of the environment, as depicted by the knowledge base package with the directives from the goal manager to create control signals to specific actuator mechanisms.

In some systems, such as an assembly cell, the externalization packages may regulate position or process control parameters according to a control scheme. In other systems auditory output or visual display may provide feedback to the user.

<sup>&</sup>lt;sup>3</sup>Perhaps this is a second knowledge base manager distinct from that monitoring the immediate state of the internalization packages.

# 1.1.2. Machine Vision

Algorithm development for the analysis of time-varying space based imagery is a prime motivator for the fabrication of a RAPIDbus system. This particular application serves to illustrate some of the characteristics of vision internalization and knowledge base packages, although console and display packages are also involved.

Vision packages are typically characterized as a pyramid, beginning with large iconic images, which are typically processed to extract a concise representation of the external environment relevant to the internal knowledge base. The knowledge base may guide the vision task by providing information from a time history of past image frames or by describing objects or situations known to the system [74, 50].

Most approaches to early vision processing, at the base of the pyramid, are highly parallel, accommodating data rates which may exceed ten million, eight bit samples per second for high resolution aerial image sensors. Many different special purpose architectures, both digital [53] and electro-optic [40], have been designed to implement operators such as convolution [15], correlation [56], spatial filtering, moments [14] and edge enhancement [15].

At higher levels in the pyramid, data rates decrease, but the computations becomes less regular. Concurrency is still possible, though at the task level, either by working on separate portions of the image, or by working on different hypothesis of system structure. For instance, in a graph matching approach [21], several tasks could start at different points on the search tree, working to convergence on a particular representation. A multitude of other high level analysis approaches are discussed in volumes such as Ballard & Brown [6], many of which are potentially adaptable to programmer dictated parallelism.

As a high level representation of the external environment forms within the knowledge package, the goal manager can begin to exercise reporting criteria, making decision as to how and when to report the results of analysis.

# 1.1.3. Assembly Assistance

Research in sensor based robot assembly cells represent a second potential application for a RAPIDbus system [61]. Within such cells, one or more manipulators may be used to accept incoming parts, join them, and pass subassemblies on.

Automated assembly may require a wide range of internalization packages including binary or grey level vision [62], acoustic, optical, electromagnetic, force, or tactile. Each of the sensors may be introduced to the system expediently using a standard interface protocol such as RS-232, GPIB, current loop, or parallel port. Preprocessors may already exist using one or more I/O bus standards such as STD bus, Qbus, or Multibus. Other than vision systems, such sensors are often low bandwidth, but numerous. Their internalization packages can often be productively formulated with a separate package bound to each sensor or group of sensors.

The centralized knowledge management package is especially useful with very diverse internalization packages. As in the vision application accented above, flexible assembly may rely on two knowledge base packages, one describing the immediate assembly environment, the second describing the assembly procedure.

At a higher level, several such assembly cells may interact under the control of a goal manager package within one tightly coupled system. Irregularities or individual job characteristics may then be passed from cell to cell through the knowledge base package.

At the externalization stage, a variety of different actuators may be required, controlling position, flow, or force at many different points. Support for standardized interface protocols is again useful in the rapid integration of existing controllers.

# 1.1.4. Design Assistance

Design automation represents a third application for a tightly coupled processor system. Project's such as Demeter at CMU are working to develop integrated design environments to assist in the translation from design specification to fabrication documents [34, 66, 8]. Although the majority of such systems fit well onto workstation or general purpose computing environments, the gate level simulation of large digital circuits presents special performance problems.

Prior to expending the effort required to fabricate either custom silicon or board level designs, it is useful to analyze their behavior. Such analysis can help to verify correctness, evaluate performance tradeoffs, and study the response to system faults. Although many design automation tasks for a large project can be handled in small pieces, simulation, by nature, often involves the entire design. Current uniprocessor-based simulators are frequently too slow to get meaningful performance statistics, or to integrate actual silicon devices with dynamic memory elements.

Figure 1-2: Mapping subsystems to separate simulation packages with inter process communication along well defined interface paths can improve simulator throughput.

Based on the pioneering work done by Lawrence Livermore Labs with SCALD [63], many design automation systems support hierarchical design descriptions with a multitude of different modules at all but the top layer, as shown in figure 1-2. At the second highest layer, communication between modules can readily be made very explicit, and is usually along clean interface boundaries.

This suggests the possibility of mapping each such module at a convenient high level to a different task, and potentially processor, for simulation. Each task simulates an event queue for a specific step interval. When the queue is exhausted, outputs are exported to other simulation tasks for event scheduling, designated signals are sent to a display task, and a clock task is given an interval completion signal. In turn the clock increments the timing and initiates the queue for the next step in each simulation task.

In this way, simulation of large digital circuits can be productively cast as a highly concurrent multitasking problem with programmer controlled parallelism and tight coupling. In the context of RAPIDbus, simulation is a support task for the efficient fabrication of new digital hardware.

# 1.2. RAPIDbus

# 1.2.1. Defining a Structure

The model of a robot system described above has strong implications for the design of an effective, very high performance machine architecture. Even at the package level, a high degree of concurrency is suggested. As three example environments indicated, each package is often further divisible into concurrent tasks. Coupling the need for high, cost effective performance with this degree of concurrency led to the choice of a multiprocessor architecture for RAPIDbus. The strong dependency between tasks suggested that low latency communication was imperative. The variety of different tasks suggested a haterogeneous processor structure.

# 1.2.2. The Goal

It is the goal of this project report to describe a multiprocessor structure supporting a multitude of diverse, heterogeneous tasks grouped into packages with a tight locality of reference. Parallelism is explicitly designated by the programmer, assisted by architectural features to support modular, strongly typed code. Underlying this goal is the hypothesis that such a structure can effectively support the development of advanced robot systems.

# Chapter 2 RAPIDbus I: Architecture and Realization

# 2.1. Why Build?

When the time comes to create a machine intended for *use* in a particular application, one begins to appreciate the observation that there are two kinds of computer architects [12]. The first spend their lives studying how to build machines, the second build machines. Each approach has strengths, each is symbiotic with the other. The first kind of architect lives in a world of paper and models, the second in a world strung together with semiconductors and unforgiving electrons. RAPIDbus I is our first step into the perils, and lessons of this second realm.

A time-multiplexed common bus was chosen as a cost-effective initial configuration connecting a small number of high-end microprocessors. At the suggestion of Rafael Bracho, we took advantage of commercial Versabus monoboard computers connected through individual interface cards onto a time-multiplexed physical bus [13]. The basic design for the time-multiplexed bus was adapted in part from an earlier design by Zoccoli [81].

A two processor system, shown in figures 2-1 and 2-2, was constructed and evaluated to provide a realistic basis for the qualitative and quantitative description presented in this

Figure 2-1: A dual height Versabus card cage was constructed to house the two processor RAPIDbus I prototype.

chapter. This background forms the basis of the evaluation described in the following chapter. More extensive details of the RAPIDbus I design can be found in CMU Robotics Institute Technical Report 82-13 [77].

# 2.2. Systems Architecture

# 2.2.1. Choosing Versabus as a Host

Versabus is a circuit-switched common bus protocol developed by Motorola to the 68000 family of microprocessors. Using an asynchronous handshaking protocol, data can be transferred on up to 32 data lines and selected by 32 address lines in a series of upward compatible steps. Multiprocessors are supported using a bus arbitration scheme controlled by a central arbiter. Vector interrupts are implementing by extending the 68000 interrupt structure to the bus.

Figure 2-2: The RAPIDbus I interface was implemented on a mother- daughter board inserted between the physical bus and a commercial monoboard computer.

In late 1981, when the processor was being selected, the 68000 microprocessor was a reasonable choice for the kind of numerically intensive computation that was foreseen in **our** application code. The 68000 allows use of 16 bit data transfer capability, with a 16 megabyte (24 bit) addressing range.

Similar results are likely using the Intel 80X86 line of microprocessors running on a Multibus with suitable modifications. Although the original Multibus was not designed for 32 bit cc mpatibility, a new draft standard, MULTIBUS II, is expected to provide 32 bit synchronous data transfer capability [70].

Versabus is specified in draft form as Motorola document M68KVBS-D4[46]. An IEEE committee has been formed to consider IEEE standardization of a similar bus protocol. Since the initial release of Versabus, market pressures have lead to the design of *i*\text{VME} bus specification, which has a protocol similar to that of Versabus, but is usually implemented on dual DIN cards using the 16 bit bus option.

Other industrial bus standards were rejected as a prototype host interface for a variety of reasons. Card size restrictions and limited bus widths eliminated the S100. Qbus did not provide a commercially available processor card with the price/performance that the VM02 offered. Tl's 9900 bus did not have a seem to have enough support or performance to be interesting. Both the VAX SBI and the Gould SEL bus were considered and rejected based on the inavailability of appropriate single board processor cards.<sup>4</sup>

### 2.2.2. PMS Level Alternatives

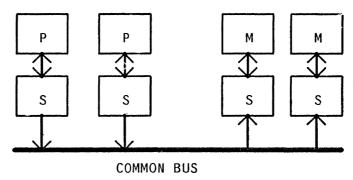

Once the decision was made to use a monoboard computer as the processor node, a variety of processor-memory-switch (PMS) [64] level structures were possible using a common bus. The simplest approach was to assign processors on one set of cards, and the memory on another set of cards (figure 2-3). All memory references are subjected to bus latency, increasing load on the interchange network.

Figure 2-3: Separation of processor and memory functions on the bus maximizes bus loading and average memory reference latency.

In order to reduce inter-processor bus contention, many monoboard computers provide local memory, either ROMS containing system software, or RAM for private data or instruction segments. Shared memory segments are still located on separate RAM cards accessible via the common bus. Access to such shared memory requires that both a read and a write operation take place on the system bus to communicate a word of data between processors (figure 2-4).

By dual-porting memory onto both the local processor and system bus, the number of

<sup>&</sup>lt;sup>4</sup>The SBI and the SEL bus are synchronous, a appealing characteristic when time-multiplexing a host port.

Figure 2-4: Addition of local memory on the processor card permits quick access to private data and instructions.

references required on the system bus decreases (see figure 2-5). The communication of data from one processor to another requires only a single bus transfer to share each word of data.

A circuit switched interchange network, which supports ortly one circuit path for the duration of a memory access, such as Versabus, has no risk of deadlock resulting from the sharing of a single interchange port between outgoing processor requests and incoming memory accesses. Performance can decline resulting from memory contention, but since the Versabus host port is only assigned to one master at a time, a situation cannot arise where respective local dual ports are simultaneously assigned to the local processor engaging in a bus transfer that requires the other dual port memory, resulting in deadlock.

Several months into the design of RAPIDbus I, after we were committed to implementing a dual VM02 prototype with dual ported memory, it became clear that the circuit switching assumptions built into Versabus would greatly complicate the overlaying of a time multiplexing interchange with multiple simultaneous paths. Since multiple Versabus hosts could simultaneously receive conflicting Versabus port grants, a serious deadlock problem was introduced. Coupled with the 68000's inability to rollback on all instructions, we were left with the possibility of either accepting bus error (time out) traps for legal accesses, or modifying the Versabus protocol on each host.<sup>5</sup>

The efficiency of each of these approaches is analyzed in the following chapter, both using a straight Versabus implementation of the common bus, and with a RAPIDbus interface card interposed between host and bus to create the illusion of several physical busses through

<sup>&</sup>lt;sup>5</sup>RAPIDbus I accepted the possibility of traps on valid requests.

**Figure 2-5:** Dual porting of the local memory can economize en bus cycles required to access shared memory.

time-multiplexing. As one expects, performance comparisons can only be made based on application dependent parameters. It is clear however that going from the first to fourth configuration above, the hardware complexity increases. Al! tests involving actual hardware were based on a pair of VM02 processors and RAPIDbus I interface cards.

# 2.2.3. The RAPIDbus I Interface

# 2.2.3.1. RAPIDbus I Concept

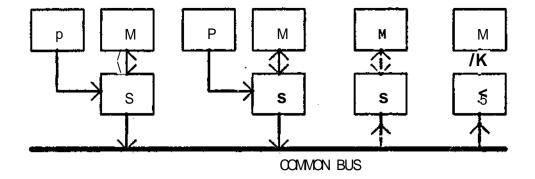

A primary goal of the RAPIDbus I protocol is to take advantage of the bandwidth differential between a single block of bulk dynamic memory, and the theoretical bandwidth which the system bus is capable of. By time multiplexing the physical backplane, each Versabus port capable of initiating a data transfer (master) is assigned a virtual bus, along which all other available RAPIDbus ports in the system may be accessed as slaves. Each master appears to have a private link from the RAPIDOus port on the interface card to the RAPIDbus ports of all other system cards. Versabus processor which share a dual-port with local memory may have to arbitrate use of their port with other masters accessing the dual-port memory.

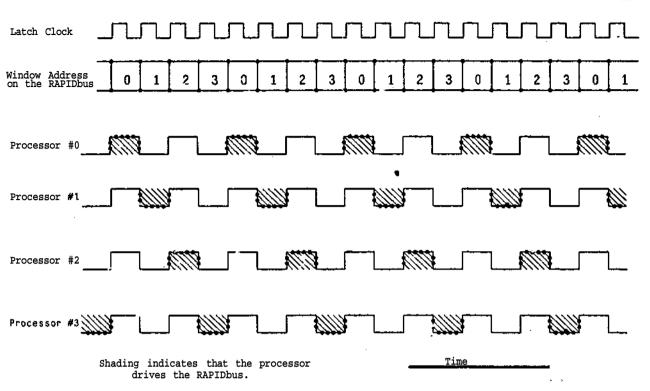

The virtual busses connecting the RAPSDbus port on each interface card are implemented using time-domain bus windows. Each interface which supports a processor is sequentially given a window during which the master interface may send a data transfer request to one or more slaves, and/or receive a response from an already activated slave. System timing is illustrated in figure 2-6. At least three windows are required to complete a data transfer. Experience with the VM02 card suggests that most Versabus cards will require several more. Thus the RAPIDbus interface card transforms between the time-multiplexed RAPIDbus windows that are pertinent to a task, and the time-static Versabus host.

Figure 2-6: The virtual bus system is implemented using bus windows to link several masters and slaves simultaneously.

Our FAST TTL implementation indicates that up to four windows can reliably be supported using an eight to ten megahertz processor. A variety of signal lines are required to implement data transfer, some of which are time-static, and \*some of which are time-dynamic, communicating during bus windows. Data and address lines are examples of lines sent on bus windows, having different values for each of the virtual busses. Other lines are time-static and are identical for all virtual busses. The interrupt lines are examples of time-static lines, interrupting a processor handling a given level independent of the virtual bus that the interrupt handler is assigned to.

A multicasting capability is supported on the interface which allows one master to write blocks of data simultaneously into multiple memory locations. Prior to a multicast transfer, the system multicast capability must be assigned to a master, and the required address generators initialized.

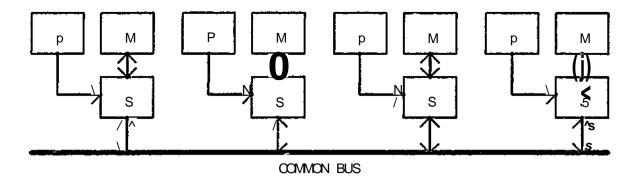

# 2.2.3.2. RAPIDbus functional modules

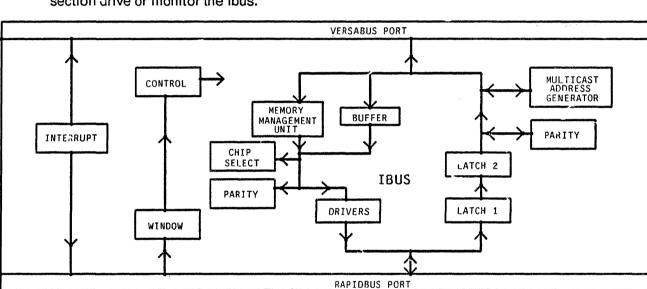

Each RAPIDbus I interface card is composed of a series of functional blocks as shown in figure 2-7. This compartmentalization of function is intended to improve the readability of a design, simplify debugging, and identify functions that lend themselves to packaging integration. The interface is composed of a window handler, drivers, latches, an address translation unit, a multicast address generator, a parity check section, a chip select section, a timing generator, an interrupt control section, and an interface controller. The Ibus links the Versabus port on the top of each interface card with the RAPIDbus port at the bottom. It comprises the address translation section, the drivers, and the latches. The Versabus port, the RAPIDbus port, the multicast address generators, the parity section, and the chip select section drive or monitor the Ibus.

Figure 2-7: Each RAPIDbus interface card is composed of multiple modules, centered around the Ibus.

The heart of the time-multiplexed bus is the window handler. Each interface port off the

# Window Handler

RAPIDbus is assigned a unique window identification number, which determines the home address, timeout interval,<sup>6</sup> and in the case of a slave, the control page address within the RAPIDbus physical address space. The window handler scans the window address bus looking for either the home window address or that of a master for whom this interface is working as a slave. Through the control register the interface can be configured so as to

recognize only one window address for slave accesses (masking).

<sup>6&</sup>lt;sub>to reduce deadlock</sub>

# Driver

The driver section is used to gate the address, data, and control lines onto the RAPIDbus during a window as directed by the control sequencer. When the control sequencer does not indicate that this interface is to drive a given backplane line in the current window, the lines are to be tri-stated. Line drive is to commence as soon as the appropriate window is recognized and continue until the next window is recognized.

### Latch

The latch section holds data at two levels. The first latches all time-multiplexed RAPIDbus lines at the end of every window. During the following bus window, these latched lines are examined for a slave reference to this interface card. If the lbus is not being requested or is in use, and a slave reference to this interface is detected, then the contents of the first level latch are held by the second level latch. The second latch also holds the bus window if the lbus is already allocated to the virtual bus currently sending the bus window held at the first level latch. Under the direction of the control section, lines can be selectively gated onto the lbus according to the function of the current ibus master.

# **Address Translation**

Data transfer exchanges must always be initiated by a master, and each master interface may optionally have an address translation unit positioned between the host processor and the RAPIDbus drivers. The function of the address translation unit is to map A8 - A23 to physical addresses PA8 - PA23. In any interface that incorporates a address translation unit, the translation must be capable of being circumvented through the control register so as to map the Versabus address directly to the RAPIDbus drivers. The lower seven address lines, A1 - A7 are supplied directly to the driver section without translation. The control register also allows switching between primary and secondary memory maps on interfaces that support memory management.

# **Multicast Address Generator**

The multicast address generator is required for all interface cards that must function as a slave during a multicast data transfer cycle. The master desiring to multicast must set the multicast request bit in its control register, asking the processor's interface to try for ownership of the multicast capability. Line twelve of the interface status register is asserted low by the interface to indicate that the multicast capability has been secured by this interface.

Prior to sending multicast transfers, the multicast address generator registers of all interfaces that are to be destinations must be loaded with the base address and the number of words that are to be multicast. For interface cards which support master and slave functional hosts, the master occupying the Versabus port must be asked to initialize his multicast address generator since the MAG registers for a master interface only appear in that master host's memory map. For slave-only interface hosts, such as a memory card, the MAG registers are mapped into the RAPIDbus physical address space.

Following write instructions to the multicast reference address will be multicast to each activated slave card until a slave's word count is exhausted or the master stops writing to the multicast address. Each activated slave depends on its multicast address generator to supply the memory address and maintain the count of words still to be transferred. The address counter is not incremented and the word count not decremented if multicast retry is asserted by any interface being multicast into before the multicast data acknowledge has gone high.

# **Parity**

The parity section generates and checks parity during master and slave transfer operations over both data and address lines. A parity error results in a retry of the transfer cycle unless the aborted instruction was part of a read/modify/write operation.

# **Chip Select**

The **chip select** section serves to direct references by the Ibus owner to the interface control page, Versabus, or RAPIDbus port. If a master reference is not to the control page, then the reference is directed to the RAPIDbus drivers. Control page references are subject to further decoding to identify the reference as a multicast, multicast control, interface control/status register, or memory management unit reference, selecting the appropriate device or in the case of the multicast, the interface RAPIDbus multicast server.

# **Timing Generation**

The timing generation section controls the timing of the interface state sequencing. This section generates the multicast and regular address strobes when the respective address lines are ready for the RAPIDbus drivers, and generates decode enables and DTACK for the interface mapped resources.

# Interrupt Control

The **interrupt control** section supports interrupt generation and interrupt handler vector requesting. This section presents to the Versabus port on the interface only those interrupts that the interface host is strapped to uniquely handle. If installed, the memory management unit interrupts at one of the levels handled by the local host. The interface host is able to generate any one of the seven levels of RAPIDbus interrupts.

Interrupt vector acknowledge operations are correctly supported, with the hardware supported restriction that only one master at a time may run an interrupt acknowledge cycle. Within an interrupt level, physical priority in the card cage dictates interrupt handling priority.

# Control Section

The **control section** knits together the other functional blocks and controls the logical state of the interface. The ownership of the lbus is decided by the control section. The interface bus error, retry, data acknowledge, and halt are generated by this section, as are timeout and retry limits. The control section contains the control/status register which allows dynamic configuration of interface parameters such as the masking address, the address translation path, and the auxiliary memory map.

# 2.3- Communications Protocol

A variety of different data transfer protocol are used in the RAPIDbus I architecture. This section serves as both a summary, and a pointer to more detailed literature.

# 2.3.1. The 68000

The Motorola 68000 forms an entire micro-coded processor on a chip. The chip must communicate with external hardware however, in order to accept instructions, read and write data, generate and handle interrupts, and respond to irregular termination conditions such as reset, bus errors, and retries. This section is concerned with summarizing the protocol for communication off chip. For detailed information, see the relevant Motorola manuals, and technical bulletins [48, 35]

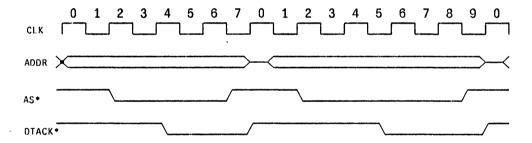

## 2.3.1.1. Memory Reference Cycles

The 68000 uses a handshaking protocol to access either byte or word operands from either memory or peripherals. Twenty-three explicit address lines are used, supplemented by three bits of function code, and two data strobes. The two data strobes, upper (A0 is low), and lower (A0 is high) are used to select either or both of the least significant bytes addressed by the sixteen megabyte address range. Long-word transfers are implemented as a pair of atomic transfer operations. The 68000 defines five significant function codes, supervisor program and data, user program and data, and an interrupt cycle. Either supervisor or user function codes, when paired with an asserted address strobe, and at least one asserted data strobe indicate a valid data transfer cycle.

A given data transfer cycle can read an operand; write an operand; or read an operand, modify it's value, and write it back as part of an atomic bus cycle. A write operation is indicated by the write line being asserted low while both address strobe and at least one data strobe are low.

Figure 2-8: Bus transfer timing relative to the processor clock for two cycles, the first in zero wait states, the second requiring an extra clock cycle.

Any data transfer operation is terminated either with data acknowledge, bus error, halt, or reset being asserted low. Normal bus cycles conclude, or read-modify-write cycles are punctuated by the assertion, and later removal, of data acknowledge. Bus error is an irregular termination which is sampled once on each microcycle during the transfer. If bus error is asserted, and halt is still inactive, then the transfer is aborted, and the microengine traps to a handler routine. When bus error is asserted in conjunction with halt, then the current memory fetch cycle is terminated, and if possible, rerun. In the current 68000, all instructions except

for test and set are capable of being rerun. Assertion of halt alone puts the microengine into a state of suspended animation from which only a reset will recover.

Motorola specifies the data acknowledge, bus error, halt, and reset for assertion a setup time before they are sampled by the internal microengine. It is interesting to note that some designs violate this setup time, with apparent impunity. A penalty is, however, paid in processor throughput, and potentially in system reliability. Since the internal micro-engine samples the data acknowledge only once during each clock cycle at and following the end of microcycle four, assertion of data acknowledge randomly with respect to the clock potentially slows down every memory reference by an average of half a clock period, or about twelve percent (relative to a zero wait state operation).

## 2.3.1.2. Interrupt Cycles

In order to efficiently respond to events asynchronous to the current instruction stream, the 68000 is designed to support vectored interrupts. Three external interrupt lines are sampled at the end of each instruction cycle. Subject to possible internal masking, an interrupt acknowledge cycle will be initiated on the data bus, denoted by an interrupt acknowledge function code. The low address represents the interrupt level which the processor is currently responding to. A pointer to the proper handler routine is returned by the interrupting device, or an interrupt vector generator working on behalf of the interrupter on the low byte of the data bus.

## 2.3.2. The Versabus Data Transfer

Shortly after the introduction of the 68000 processor, Motorola released Versabus as a bus protocol optimized for their processor interface. Versabus was intended to support a tightly coupled system of "data processing, data storage, and peripheral data control devices" [46],

<sup>&</sup>lt;sup>7</sup>Manufacturers and those using their parts have often designed bus protocols around a new processor, The S100 bus is based on an 8080, the Apple bus on the 6522, the Qbus on (he LSI-11, and the Multibus on the 8086, to cite a few.

## 2.3.2.1. Bus Arbitration

Each Versabus system has a system controller which is responsible for Versabus arbitration among other duties. A requester desiring use of the bus pulls one of five prioritized, open-collector bus request lines **BR0-BR4**. A special requester, the emergency requester, has an additional, high priority request line. If a request is submitted at a higher priority than the current bus master, the system controller's arbiter can assert the **bus** clear line, instructing the current user to free the bus. Some Versabus masters automatically release the bus after a single data transfer, others hold the bus for multiple transfer cycles, and some even hold onto the bus until ordered to release by the **bus** clear signal.

After the current bus master has removed the BBSY line, the arbiter grants the bus to the highest priority active request level following an arbitration delay. In some implementations this arbitration process can occur while the preceding data transfer operation is concluding. Since multiple potential bus masters may have made a bus request on the same line, the arbiter sends the **bus grant** signal down one of several daisy chains where it is passed along until it encounters a card which requested the bus at this level. Such a card traps the bus grant, and begins to drive the BBSY signal. The arbiter receives this BBSY signal, and removes its bus grant.

#### 2.3.2.2. Data Transfer

After bus mastership has been granted, a processor begins by asserting the address, function code, address strobe, and data strobes as appropriate to the width of the data transfer (see a description of the 68000 above for details). All potential slaves scan the address and function code lines, waiting for a reference that addresses their resources. The selected slave arbitrates for use of the dual-port RAM if needed, conveying the address bits to the memory or peripheral logic.

If the write line is high following assertion of data strobes, then a read operation is in progress. After the operands are available, and gated onto the Versabus, the slave drives the data acknowledge line low, causing the master to latch the data and release the lines it is driving. In the case of a write operation, with the write line low, the memory latches in the data, and returns data acknowledge to the processor, causing the processor to release the lines that it is driving. In the case of a read/modify/write operation, the address strobe remains assert after data acknowledge comes back from the read operation, continuing through the write cycle. Any data transfer cycle can be terminated if the BERR line is asserted.

Optionally, parity is checked for both address and data transfers, although no current Versabus processor cards are known to support this capability. The halt Sine is no longer carried out to the Versabus, making retry operations impossible from the bus with unmodified Versabus cards. A variety of bus width options are enumerated in the specification, covering data paths of eight, sixteen and thirty-two bits, and address bus widths of sixteen, twenty-four or thirty-two bits.

# 2.3.2.3. Interrupt Handling

The 68000 vectored interrupt capability is brought out to the Versabus, using a cycle similar to a read data transfer. The handler is granted bus mastership, asserts address and data strobes, and conveys the interrupt level being serviced on the least significant bits of the address lines.

In order to support multiple potentially interrupting Versabus cards at the same level, the interrupt lines are daisy-chained similar to the bus grant lines. Only the first card which interrupted at the level being acknowledged by the daisy chain generates a vector. Thus within a given interrupt level, physical location of the interrupter determines priority of service.

## 2.3.3. The RAPIDbus I Data Transfer

The RAPIDbus I data transfer protocol is based on an adapter which sits between the Versabus port of a standard Versabus card, and the physical bus, converting between the time-static bus seen by the Versabus card and the time-multiplexed busses implemented on the physical RAPIDbus backplane. On each interface the Ibus connects the Versabus and RAPIDbus port. This bus resembles a Versabus to the Versabus host port, with suitable arbitration between host and requests that may come from the RAPIDbus port.

## 2.3.3.1. Data Transfer

Once the Versabus port has requested and been granted mastership of the Ibus, some versions of the interface card translate the address using a Motorola 68451 memory management unit. Later versions of the processor card incorporate the memory management unit at the processor, and the interface MMU is not supported. The potentially translated address is decoded for routing either to MMU control registers, the interface control register, multicast address registers, or RAPIDbus resources.

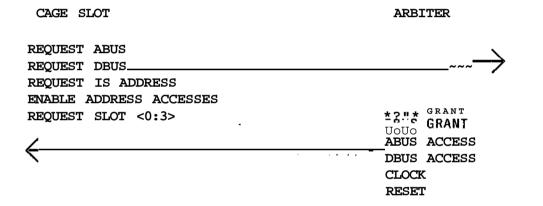

A decoded address which maps to the RAPIDbus waits until the fixed time-slot allocated to

this interface card, then drives the backplane with the full address, function code, and control lines. Other interface cards examine the backplane for references to their resources. Until the full transfer operation is complete, all data transfer will occur on the home window of the originating processor.

At some point the proper memory or peripheral card becomes available, latching in the data transfer request so as to present it in a time- static manor to the slave Versabus card, where it appears as a normal transfer operation. The data is similarly exchanged using the initiating processor's home window. To the two Versabus ports involved, the transfer operation completely resembles a standard Versabus transfer.

As the evaluation net model which follows will make clear, the current implementation permits four such exchanges to occur simultaneously given four processors, four memory or peripheral cards, and an appropriate addressing pattern. Each transfer is however slightly longer than a single conventional Versabus transfer would be as a result of the additional switching that is taking place. Data and address parity is checked on all transfers, with errors handled via a processor rerunning the transfer for all but a 68000 test and set instruction.

## 2.3.3.2. Interrupt Handling

Interrupt vector operations are more complex than with a straight Versabus. The interrupt vector request and return are handled as a data transfer operation, with a valid address corresponding to the interrupt level which the interrupter generated. Problems arise in the interrupt acknowledge daisy-chain. Unfortunately there is no simple way of multiplexing a daisy chain at high speed. Since the interrupt acknowledge is not a very frequent bus cycle, an interlock mechanism allows only one of the four virtual busses to run an interrupt vector request cycle at one time.

## 2.3.3.3. Multicasting

The Multicast capability is an enhancement not supported under Versabus, which allows one master to simultaneously write into multiple destination memory locations assisted by address generators located on the interfaces of the destination cards. Only a single virtual bus can own the multicast capability at any one time in order to simplify the complexity of the address generators and share multicast acknowledge lines.

Hardware arbitrates the multicast capability among any busses desiring use of the

capability, based on interface control register requests. As soon as the previous multicast master releases the capability, a bit in the interface control register will indicate a grant to the next requesting interface, allowing the new multicasting master to acquire the required capability.

The master must then initialize the multicast address generators in each of the destination cards, specifying both the number of words to be transferred, and the base address. If the destination is a memory card, the register can be written directly. If the destination is located on a dual port processor card, then the initialization must be requested from the local processor, perhaps through an interrupt.

As soon as all requisite address generators are initialized, the master can initiate transfers by writing to a special multicast control address which is decoded on the local interface card. With the overhead described above, it is clear that the multicast capability is only useful when large blocks of data are to be transferred. As with standard data transfer operations, parity is always checked. Parity failure results in a retry operation affecting all active multicast cards.

# 2.4. Evaluation Net Modeling

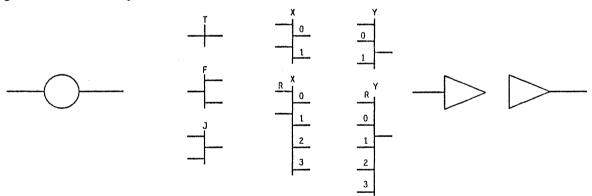

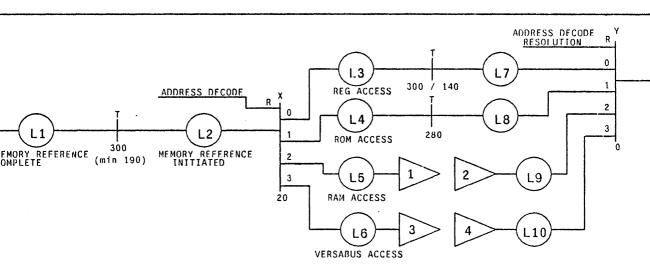

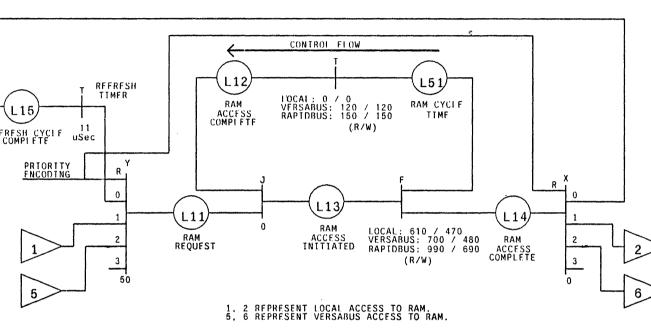

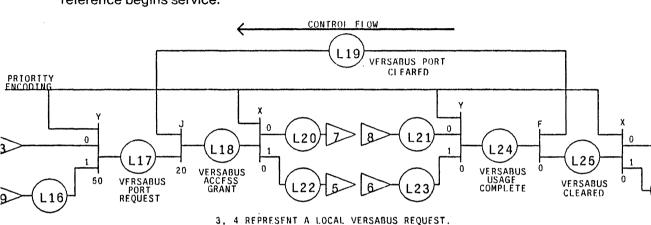

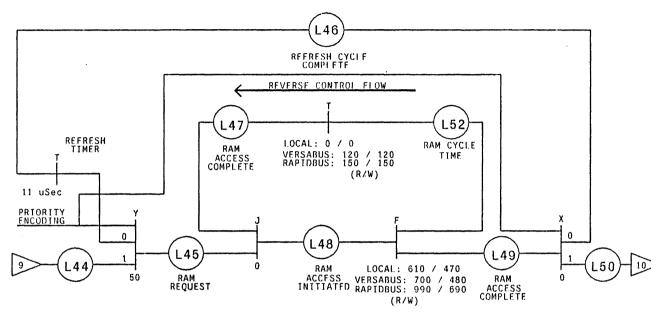

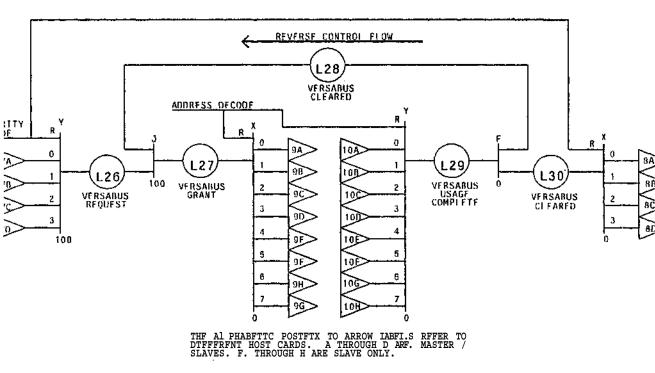

## 2.4.1. Use of Evaluation Nets for Hardware Modeling

Evaluation network [ENET] notation is a convenient method of representing control flow in both hardware and software systems. Here it is used to provide a model of the RAPIDbus I multiprocessor system. Use of enet notation allows critical timing paths in the control schema to come to the forefront in preparation for performance analysis and system optimization. Once an enet model has been devised, translation to a computer simulation can be made largely automatic. All timing information noted on the graphs was derived from logic analyzer traces run on actual hardware with the exception of the memory-only card, which used times extrapolated from a working VM02 and a memory card print set.